## BIT-SLICE MICROPROCESSOR DESIGN

· ·

·

.

## BIT-SLICE MICROPROCESSOR DESIGN

### John Mick

Engineering Manager Systems and Applications Digital Bipolar Products Advanced Micro Devices

### **James Brick**

Manager of Systems and Applications AM2900 Family Advanced Micro Devices

### **McGraw-Hill Book Company**

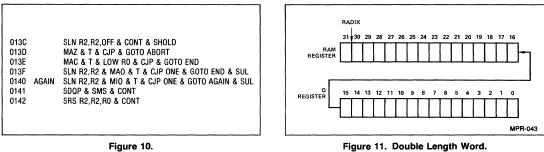

New York St. Louis San Francisco Auckland Bogotá Hamburg Johannesburg Madrid Mexico London São Paulo Montreal New Delhi Panama Paris Sydney Tokyo Toronto Singapore

Advanced Micro-Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The authors and the company assume no responsibility for the use of any circuits described herein.

#### Library of Congress Cataloging in Publication Data

Mick, John.

Bit-slice microprocessor design.

Includes index. 1. Bit slice microprocessors—Design and construction. I. Brick, James, joint author. II. Title. TK7895.M5M44 621.3819'535 80-10610 ISBN 0-07-041781-4

Copyright © 1980 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

234567890 KPKP 89876543210

Note to the Reader: Advanced Micro Devices cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an Advanced Micro Devices product.

# CONTENTS

Preface vii Acknowledgments vii Chapter I Computer Architecture 2 Chapter II Microprogrammed Design 12 Chapter III The Data Path 92 Chapter IV The Data Path—Part II 130 Chapter V Program Control Unit 190 Chapter VI Interrupt 206 Chapter VII Direct Memory Access 208 Chapter VIII HEX-29 258 Chapter IX Super Sixteen 318 Index 385

•

## PREFACE

New integrated circuits are usually accompanied by a wealth of theory and data sheets. Shortly thereafter follow the applicacation notes. The introduction of microprogrammable LSI parts, such as the Am2901 and subsequent ICs in the family, adhered to this pattern. We thought this was adequate in light of the previously successful introduction of fixed-instruction-set MOS microprocessors, which were more complex.

However, bit-slice microprocessor design proved more formidable than first realized. One reason was the intimate relationship between parts. These designs required the designer to pick and choose parts: How many slices are needed to do the job? Which microprogram sequencer and/or controller to select? Is a carry lookahead generator needed? And on, and on and.... All these devices had to play together; no single device was complete by itself.

For this added up-front design effort, the user got blazing speed and the utmost flexibility. The latter proved the second hinderance to easy designing. Users now had to design the instruction set as well as the hardware and applications programs. They no longer had the luxury of a fixed-instruction set. On the other hand, they could eliminate unnecessary instructions, easily modify or add instructions at a later date or emulate the existing instruction set of a slower CPU.

Complicating matters was the fact that the 2900 family did not spring whole into the world. Parts were introduced and redesigned over a period of years as engineering and processing resources could be brought to bear. This evolutionary process still goes on.

To alleviate matters, Advanced Micro Devices announced a nine-part course in microprogrammable microprocessing, each part to stand alone but to build logically upon the preceding part. And, because engineering talent is our most important resource, this course was to unfold over a 22-month period.

Since completion of the course, there has been no diminishing in demand for information on the material covered. In fact, the market for bipolar microprogrammable LSI parts doubled in each of the previous two years and showed no signs of slowing. So, as our copies of individual course materials dwindled, we thought it only natural to bring them all together under one cover. This book is the result.

We think the extraordinary time and effort was well worth it.

#### Acknowledgments

The authors wish to thank members of Advanced Micro Devices' bipolar applications department for their contributions to various chapters in this book. In particular we would like to thank Steve Cheng, Vernon Coleman, Mike Economidis, Jerry Gray, Jack Hong, Mike Miller, Warren Miller, Bob Schopmeyer, and Moshe Shavit.

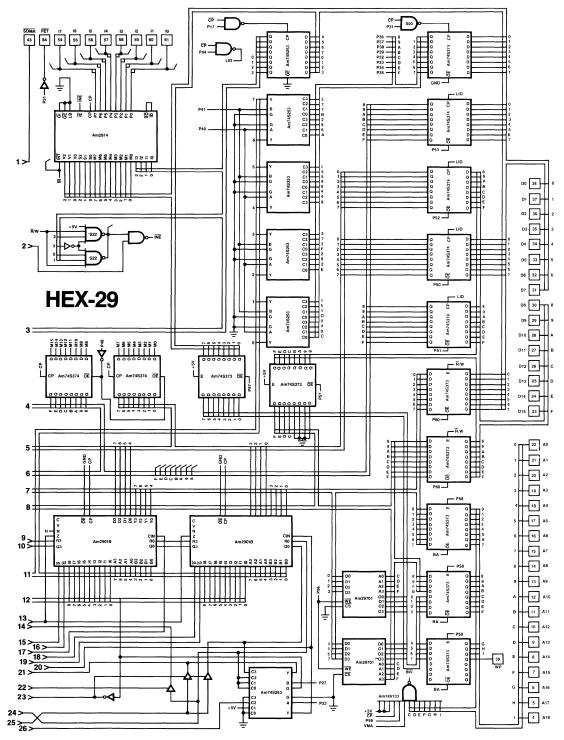

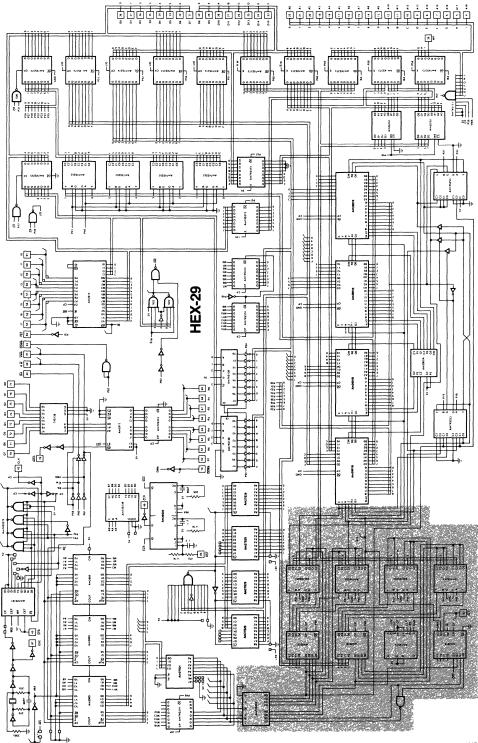

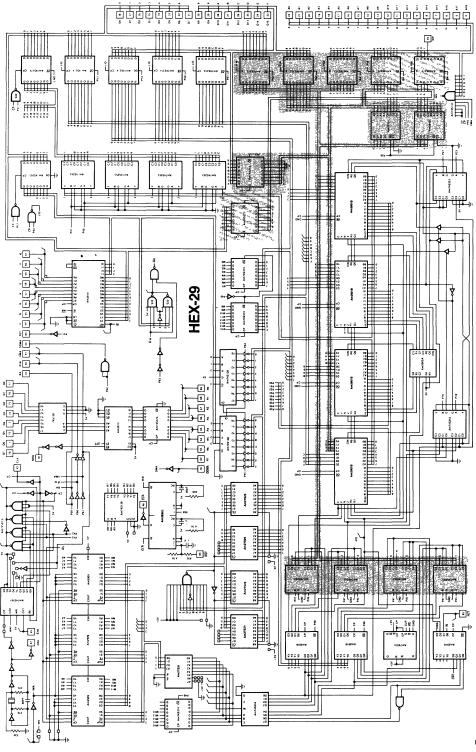

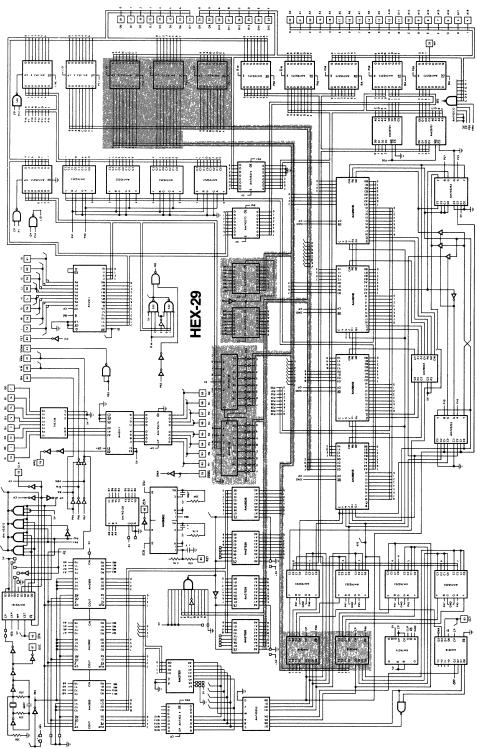

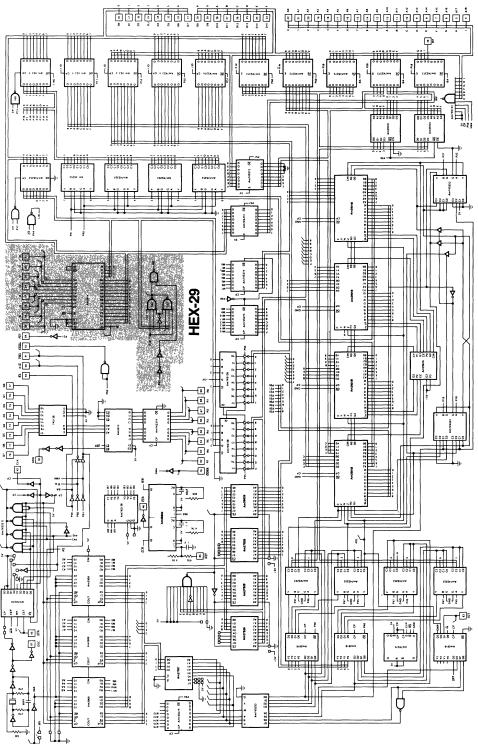

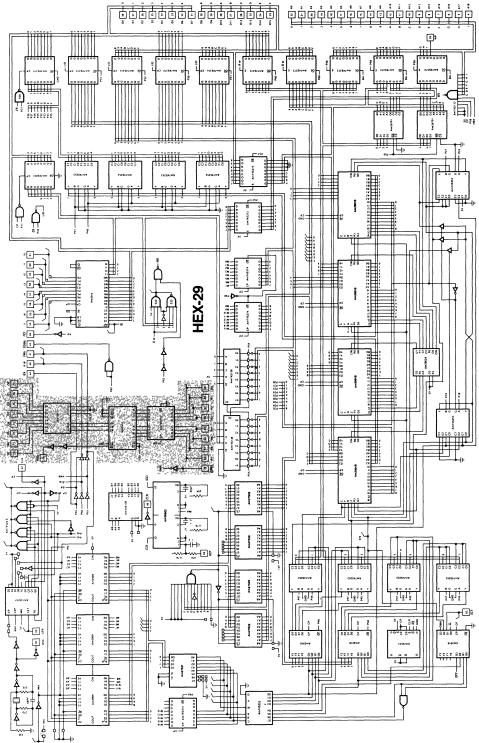

We would also like to thank Mike Simmons and Lee McDonald of Monterey, CA, for allowing us to use their HEX-29 microprogrammable microcomputer in Chapter VIII. .

{

BIT-SLICE MICROPROCESSOR DESIGN

Chapter I Computer Architecture

#### PREFACE

In this introductory Chapter we intend to:

- 1). develop a common terminology for future chapters.

- 2). introduce several stored-program-computer design topics.

- 3). define some of the computer architect's problems (which will be solved in the subsequent chapters).

In order to achieve these goals, we will start with computer basics. It should be stressed that approaches and solutions can be chosen which are different from the ones described in this and the subsequent chapters. However, the general ideas described will be appropriate to gain familiarity with the microprogrammable bit-slice devices in order to use them in any design configuration.

#### BACK TO THE BASICS...

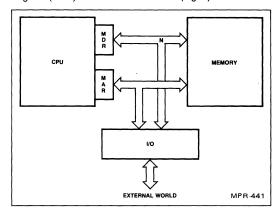

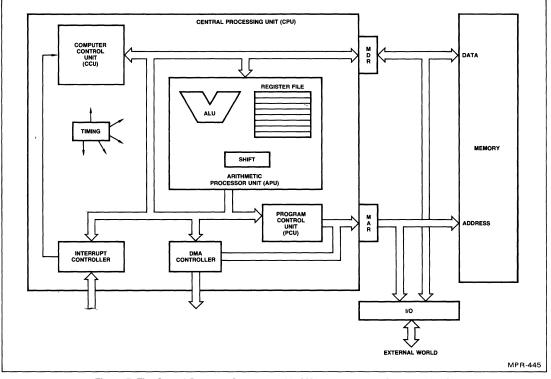

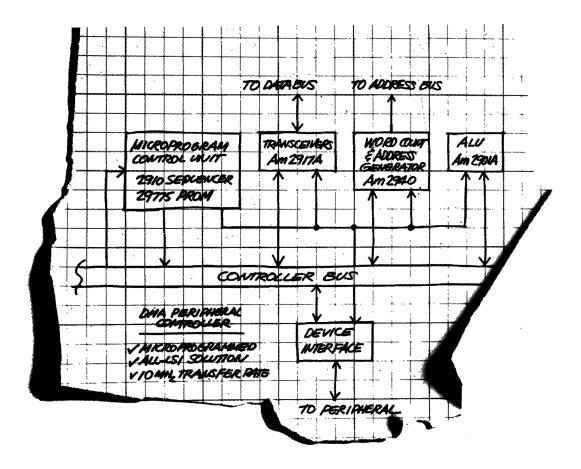

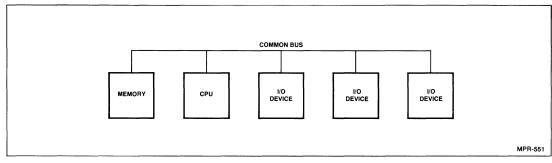

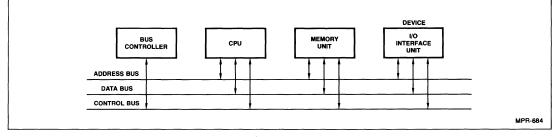

A STORED-PROGRAM-COMPUTER is defined as a machine capable of manipulating data according to predefined rules (instructions), where the program (collection of instructions) and data are stored in its memory (Fig. 1). Without some means of communication with the external world, the program and the data cannot be loaded into the memory nor can the results be read out. Therefore, an input/output device is required as shown in Fig. 2.

Figure 1. Basic Definition of a Stored-Program-Computer.

Figure 2. I/O Added to the Basic Stored-Program Computer.

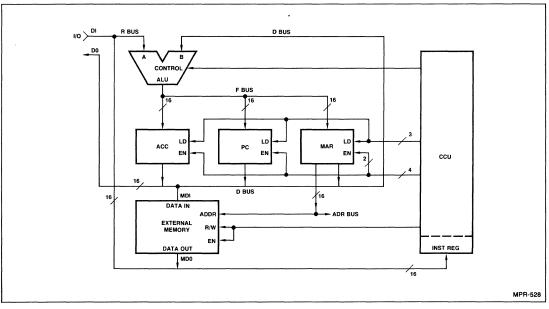

The memory is usually organized in words, each containing N bits of information. A unique address is allocated for each word which defines its position relative to other words. The Central Processor Unit (CPU) usually reads or writes one word at a time by addressing the memory and then when the memory is ready, reading the contents of the word or writing new contents into that word. To perform this operation, two registers are usually used: The Memory Address Register (MAR), which contains the address and the Memory Data Register (MDR) which contains the data (Fig. 3).

Figure 3. MAR and MDR Depicted for a Stored-Program Computer.

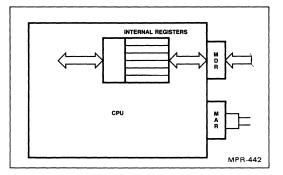

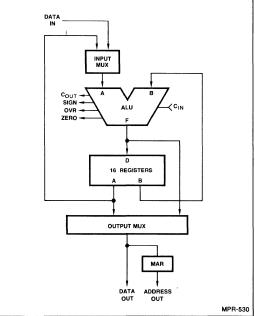

Since accessing a memory (reading from it or writing into it) is usually a relatively slow procedure, it is advantageous to have a few memory locations inside the CPU which can be read from or written into very fast. These locations are usually called Accumulators or Working Registers. Having these fast access registers inside the CPU (Fig. 4) enables many operations to be carried out without referring to the memory (through the MAR and the MDR) and therefore these operations are executed faster.

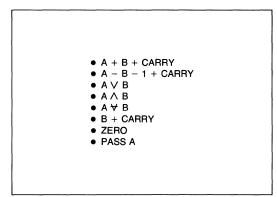

The unit which actually performs the data manipulation is called the Arithmetic & Logic Unit (ALU). It has two inputs for operands and one output for the result. It usually operates on all the bits of a word in parallel. The ALU can perform all or part of the following operations:

| Arithmetic | Logical    |

|------------|------------|

| Add        | OR         |

| Complement | AND        |

| Subtract   | XOR        |

| Increment  | NAND       |

| Decrement  | NOR        |

|            | XNOR       |

|            | Complement |

In some architectures, one of the operands must always be in a special register (accumulator) and the result of the ALU operation is always transferred to this register. In a more general CPU, any two of the internal registers can contain the operands and the result of the ALU operation can be transferred to any one of them.

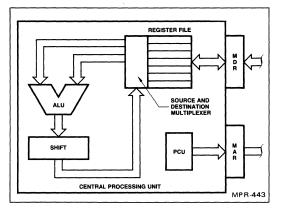

Another very useful feature of a CPU is the ability to shift the contents of a register or the output of the ALU one or more bits in either direction as shown in Fig. 5.

Figure 4. CPU with Internal High Speed Registers.

Figure 5. ALU and Shifter Added to the CPU Design.

We now have the elements to do any data manipulation required but we still need a unit which can properly set the MAR in order to find the next instruction of the program in the memory and to find its associated data. This unit is called the Program Control Unit (PCU) and its role is to load the MAR with the correct address in order to find the next instruction or data item or to point to a memory location where a data word should be written.

Often, the program steps (instructions, data) are written in the memory in consecutive locations, starting at address zero or at any other predefined address. The PCU can simply be incremented after each memory access thereby pointing to the address of the next instruction or data item. This counter-type PCU has very little flexibility. Sometimes we wish to change the "normal" flow of the instructions, particularly if we want to enable our computer to "make decisions" according to conditions prevailing at the current execution point. For example, we may want to execute one of two different sequences of instructions depending upon the result of the last operation performed. This is accomplished by loading the MAR with a new value (the address of the next instruction to be executed) rather than incrementing it. This operation is called a BRANCH or JUMP and can be unconditional (which allows execution of a non-contiguous string of instructions) or conditional (depending, for example, on whether the last operation's result was zero or not, was negative or positive, true or false, etc.).

Even more flexibility can be achieved by using a stack (a group of temporary internal or external memory locations) to store vital data. A stack pointer is used to address the memory location currently at the top of the stack. Indirect and relative addressing and other sophisticated addressing modes (all of which can be handled by the PCU) will be discussed later. Meanwhile, Fig. 5 shows the PCU as a part of the CPU.

Executing an instruction in our computer now requires the following steps:

- a). The PCU loads the address of the next instruction to the MAR and signals to the memory that a Read is requested. Incidentally, the PCU may be as simple as a Program Counter equal to the address width. The memory loads the MDR with the contents of the location addressed.

- b). The CPU decodes the instruction: i.e., (assuming operands are in internal registers) selects the proper registers to feed the ALU, selects the proper function to be performed by the ALU, sets up the shifter to displace the result, if required, and selects the register in which the result should be stored.

- c). The ALU performs the function desired.

- d). The result is loaded into the destination register.

- e). The result is also examined to determine whether a BRANCH is to be performed.

- f). The PCU calculates the address of the next instruction, (usually called a "FETCH").

This procedure becomes more complicated if the operands are not stored in the internal registers or if the result is not to be stored in one of them. Let's take an example instruction using relative addressing:

"Take the first operand from the location specified by the sum of the word after this instruction (immediate) and the contents of register R1; take the second operand from the location specified by the sum of the second word after this instruction and the contents of R2; add the two operands and place the result in the location specified by the sum of the third word after this instruction and the contents of register R3. Then execute the instruction located at the address, which is the sum of the fourth word after this instruction and the contents of register R4 if there is a carry resulting from the addition. Otherwise continue sequentially".

The steps required to execute this instruction are as follows:

- a). The PCU loads the address of the next instruction to the MAR, signalling to the memory that a Read is requested. The memory loads the MDR with the contents of the location addressed.

- b). The CPU decodes the instruction, i.e., initiates the following steps.

- c). The PCU is incremented and the next word is read from the memory.

- d). Register R1 and the MDR are selected as source registers, MAR is the destination register.

- e). The ALU performs "ADD" and the result is placed in the MAR.

- The first operand is fetched from the memory and placed, for example, in R5.

- g). The PCU is incremented and the next word is read from the memory.

- h). Register R2 and the MDR are selected again as source registers and MAR as the destination.

- ı). The ALU performs "ADD" and the result is placed in MAR.

- j). The second operand is fetched from the memory and is placed, for example, in R6.

- k). The PCU is incremented, the next word is read from the memory.

- Register R3 and the MDR are selected as source registers, the MAR as destination.

- m). The ALU performs "ADD" and the result is placed in the MAR, which now points to the location where the sum of the operands should be stored.

- n). Registers R5 and R6 are selected as sources (they contain the operands), MDR is now the destination.

- o.) The ALU performs "ADD" and the result is placed in MDR.

- p). A memory write cycle takes place and the contents of the MDR is stored at the desired address.

- q). The carry is examined to determine the next step to be performed. Assume there is no carry.

- r). The PCU is incremented twice (in order to skip the fifth word of the present instruction). It now points to the address of the next instruction.

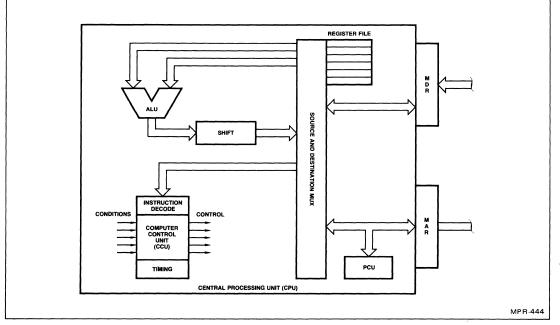

As can be seen, 18 steps were used to perform a single addition using this complex relative addressing scheme. Obviously, our CPU needs some kind of "coordinator" which can:

- 1). Decode an instruction fetched from the memory.

- 2). Initiate the proper cycle of steps to be performed.

- 3). Set up the various controls for each step.

- 4). Execute the steps in an orderly sequence.

- Make decisions according to the state of various signals (conditions).

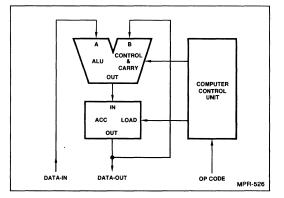

We will call this coordinator the Computer Control Unit (CCU) and it is depicted in Fig. 6. Our CPU is now complete (more or less) and we will go into more detail later.

#### THE MEMORY

Let's now discuss the memory. The information stored in the memory is organized in words, where each word consists of N bits. N may be as small as 8 for very simple processors or as large as 64 in more powerful machines. The most common memory width for minicomputers is 16 bits. The number N is called the width of the memory and the number of bits in the MDR is obviously also N; equal to the width of the memory.

The depth of a memory is the number of words it contains. With a MAR having k bits,  $2^{k}$  consecutive memory locations can be addressed. The addresses start from zero and range through  $2^{k}$ -1.

The read access time of a memory directly accessible by the CPU is the time needed from stable address at the memory until the data is properly stored in the MDR. This access time depends on the type of memory used and can be as low as a few tens of nanoseconds and as large as several microseconds. Using high speed memory improves the performance of the computer as less time is wasted waiting for the memory to respond. In general, faster memories are costly, take more PC board area and use more power which results in more heat. A 32 bit wide, 2K (2048) word memory with 50 nanosecond access time may need 10 amps from the +5V power supply and may require a board area of 10" x 6". Yet this is a very small memory space.

It is usually not justified to have very large high-speed memories. Not all the programs and associated data need to reside in this memory at once. We may have the current program (or only a part of it) in the memory while other programs or data files can reside elsewhere and be brought into memory during the appropriate part of the program when needed.

Figure 6. A Computer Control Unit (CCU) Included in a CPU.

- 1). very large capacity

- 2). non-volatile (retains the information when not in use)

- 3). not randomly accessible

- 4). long access time

- 5). inexpensive (per bit)

Usually, Bulk Memory devices are serially accessible, i.e., the access time for the first word is large, but then consecutive words can be accessed relatively fast.

In a later chapter the most efficient process of communication between the main and the bulk memory, called the Direct Memory Access (DMA), will be discussed in detail.

#### THE EXTERNAL WORLD

In any useful machine, some means of communicating with the external word is needed. It may be a keyboard, a CRT, a card reader, a paper tape punch or, in a process controller, reading sensors or positioning actuators. The common denominator of almost all of the input/output devices is that they are much slower than the CPU and therefore a timing problem arises; the CPU must know when the I/O device is ready for data transfer. Usually, a signal is sent by the device to the CPU in order to draw its attention. The CPU now can do one of two things:

Test this signal periodically and when it is present, jump to a program which handles the data transfer. This type of operation is called "Polling". This technique has two major drawbacks: First, appreciable computer time is spent performing these periodic tests where most of them will fail (no "Ready" signal present). Second, the recognition by the computer CPU of the appearance of a signal is delayed until the CPU arrives at this device in its polling sequence.

Imagine what will happen if there are a large number of I/O devices. Long latency times (delays) will occur if many I/O devices are busy simultaneously.

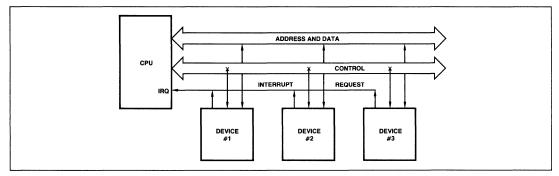

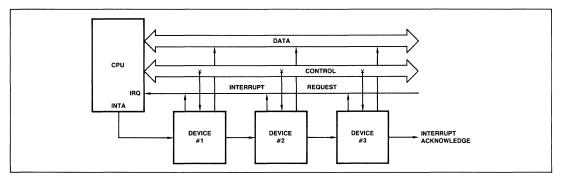

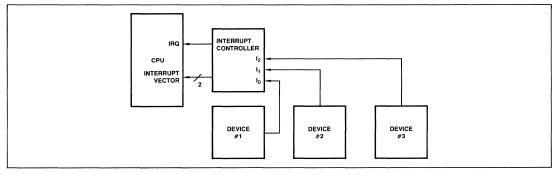

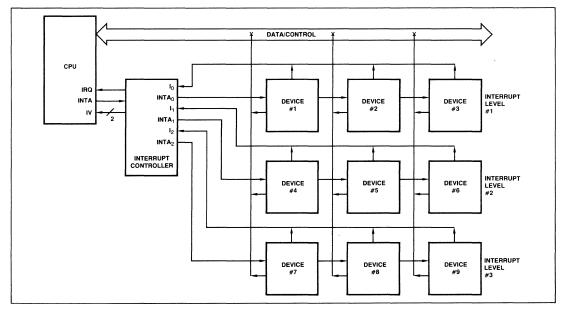

2). Include some hardware in the CPU which can sense the presence of a "Ready" signal and interrupt the normal flow of the instructions and force the computer to "Jump" to the I/O service program whenever there is a request. It can even send the CPU to different programs according to the I/O device whose "Ready" flag was detected and even establish priority among the different devices if more than one device would like to have the CPU's attention at the same time. Moreover, under program control, this circuitry can ignore some or all of the signals if the computer CPU must not be interrupted at that time. Obviously by paying the price of very little hardware, we gain enormously in computer performance. We will call this hardware the "Interrupt Controller" and will discuss it thoroughly later.

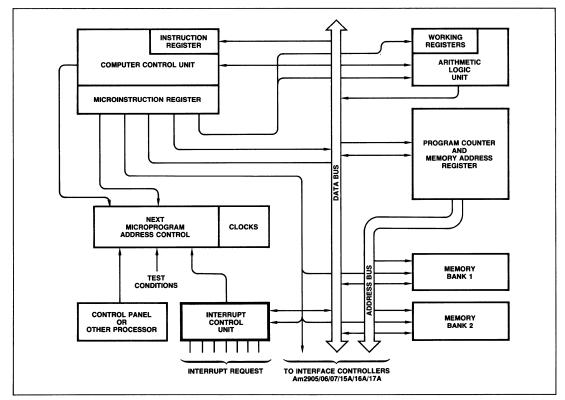

Our computer is now depicted in Fig. 7. We have included the ALU, the internal register file and the shift circuit in one block, which we call the "Arithmetic Processor Unit."

In the following pages and in the subsequent chapters, we will deal in more detail with each area of the machine.

Figure 7. The Stored-Program-Computer with DMA and Interrupt Control Added.

#### A WORD ABOUT THE INSTRUCTION SET

The internal architecture of the CPU depends to some extent on the instruction set the computer is to execute. If the instruction set is large, some of the instructions usually are more complicated and the computer is more powerful, faster and more efficient. On the other hand, the internal circuitry is also more complicated. Some examples of these tradeoffs are as follows.

#### **ALU Processing Capability:**

Although with three basic functions (add, complement, and OR/AND) all the arithmetic and logic operations can be performed, most processors are built to perform subtract, NAND, XOR, etc. This is perhaps the most outstanding example of how performance and speed can be gained with little penalty on the complexity of the machine. With the added features an XOR operation can be performed in one instruction instead of 5.

#### Data Movement:

Let us assume 4 different computers whose data movement capabilities are described below:

**Machine A).** A word can be read from the memory and loaded into Register A only. The contents of Register A can be written into the memory, or can be moved into any other register. The contents of any register can be copied into Register A.

Machine B). The contents of any register can be copied into any other register or it can be written into the memory. A word read from the memory can be loaded into any register.

Machine C). As B above but with the added capability to read from one location in memory, to write that word into another location in memory.

Machine D). As C above and also the memory-to-memory operation can be performed on consecutive addresses repetitively. The number of word transfers (or upper and lower address limits) are specified by the instruction.

Machine A has very limited data movement capability. In order to perform an operation on two operands residing in the memory, we have to:

- 1). Bring the first operand from the memory into Register A.

- 2). Copy it into another register.

- 3). Bring the second operand into Register A.

- 4). Perform the operation required (result in A).

- 5). Store the contents of Register A into the memory.

If consecutive operations are required with several partial results, the drawbacks of machine A become more annoying, especially if the number of internal registers is small.

Moving a data block from one location in the memory to another location can be performed by one instruction in computer D, but requires the transfer of each word first to an internal register then to the new memory location in machines A, B (two instructions for each word transferred).

Obviously the decoding, multiplexing and sequencing of the computers grow in complexity as we proceed from machine A to machine D. We trade the complexity of hardware versus the software (programming), speed and performance.

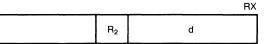

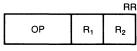

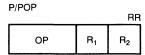

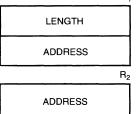

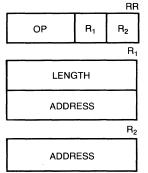

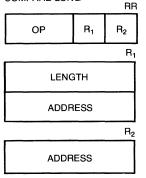

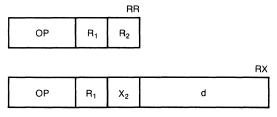

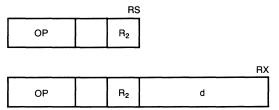

#### Addressing:

The operands for an operation can be found in several ways:

- The operand is an explicit part of the instruction (Immediate)

- The address of the operand is an explicit part of the instruction. (Direct)

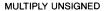

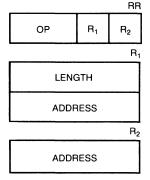

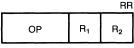

- The address of the operand is in an internal register; the register itself is specified by the instruction. (RR)

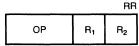

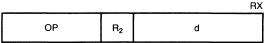

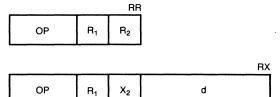

- The address of the operand is the sum of the contents of an internal register (specified by the instruction) and a number (called the displacement) which is an explicit part of the instruction. (RX)

- The contents of an internal register are added to a number found in an address specified by the instruction. The sum is the address of the operand. (Indirect)

- The contents of an internal register are added to a number which is an explicit part of the instruction. The sum points to the location where the address of the operand is written. (Indirect)

- The contents of an internal register are added to a number which can be found at the location explicitly specified by the instruction. The sum thus formed points to a location where the address of the operand is written.

- Etc.

Many other schemes can be formed by combining the above operations or by chaining them. In every case an "Effective Address" must be found by calculations and/or memory references. Again, we can gain performance by using more sophisticated addressing schemes but we will pay for it by adding complexity to our machine, especially in its control portion.

#### TIMING, SEQUENCING, CONTROLLING

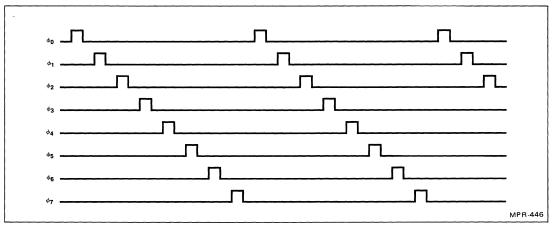

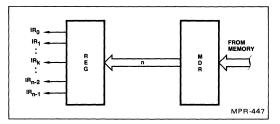

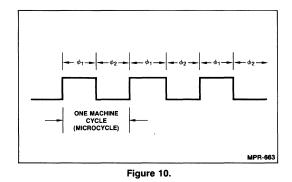

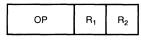

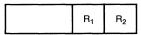

In the previous paragraphs we have shown that we can gain performance in our computer by having a more complicated instruction set but more complex hardware is required, usually in the CCU. We have also shown an example for an "Add" operation which required 18 precisely controlled steps. Even if we assume that some of them can be performed simultaneously, we will need a multiphase clock to control these steps - something like that shown in Fig. 8. We can now load an instruction register at the beginning of an instruction with the first word of the instruction (the OP CODE) as is shown in Fig. 9. Using the outputs of the Instruction Register (IR<sub>0</sub> to IRn-1), the different phases of the clock and the various condition inputs to the CCU, we can now try to write the logical equations which should satisfy all of the steps of all the instructions of our instruction set. Then use Karnough maps or other techniques to reduce these equations and finally realize them using AND, OR, INVERT gates and Flip Flops. Simple, isn't it? Imagine the complexity of a sophisticated computer and the debugging process it needs!

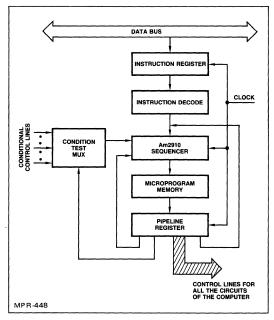

The question posed immediately is: Isn't there a more organized and more easily understandable way to do that? Or, perhaps, can we have some processor do the job for us? Can't we have some kind of "micro-machine" which can take care of all the timing, sequencing and controlling jobs of our computer – a computer inside the computer? With the advent of the Am2900 family – new Bipolar LSI devices – the answer is: Yes, we can!

Figure 8. An 8-Phase Clock.

Figure 9. The Instruction Register Bits.

Figure 10. The Micromachine.

#### THE MICRO-MACHINE

What we need is essentially a machine which can execute a number of well defined sequences. But, remember that this is exactly the purpose of a stored program computer. The only difference between our micro-machine and a general purpose computer is that in the general purpose computer the program to be executed is changed from task to task, while in our micro-machine it is fixed. This allows the use of PROM for its memory instead of the RAM needed in the general purpose (GP) computer. Our Computer Control Unit (CCU) using this micro-machine may now look like Figure 10.

Basically, a microprogrammed machine is one in which a coherent sequence of microinstructions is used to execute various commands required by the machine. If the machine is a computer, each sequence of microinstructions can be made to execute a machine instruction. All of the little elemental tasks performed by the machine in executing the machine instruction are called microinstructions. The storage area for these microinstructions is usually called the microprogram memory.

A microinstruction usually has two primary parts. These are: (1) the definition and control of all elemental micro-operations to be carried out and (2) the definition and control of the address of the next microinstruction to be executed.

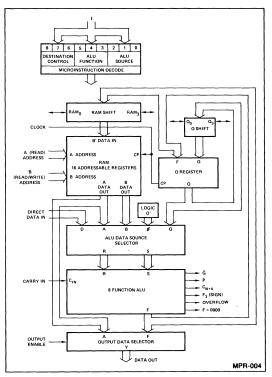

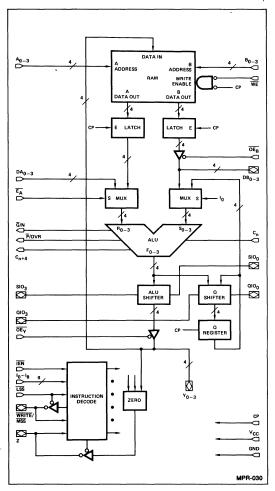

The definition of the various micro-operations to be carried out usually includes such things as ALU source operand selection, ALU function, ALU destination, carry control, shift control, interrupt control, data-in and data-out control, and so forth. The definition of the next microinstruction function usually includes identifying the source selection of the next microinstruction address and, in some cases, supplying the actual value of that microinstruction address.

Microprogrammed machines are usually distinguished from non-microprogrammed machines in the following manner. Older, non-microprogrammed machines implemented the control function by using combinations of gates and flip-flops connected in a somewhat random fashion in order to generate the required timing and control signals for the machine. Microprogrammed machines, on the other hand, are normally considered highly ordered and more organized with regard to the control function field. In its simplest definition, a microprogram control unit consists of the microprogram memory and the structure required to determine the address of the next microinstruction.

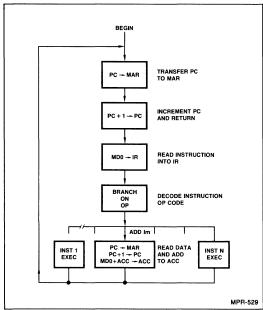

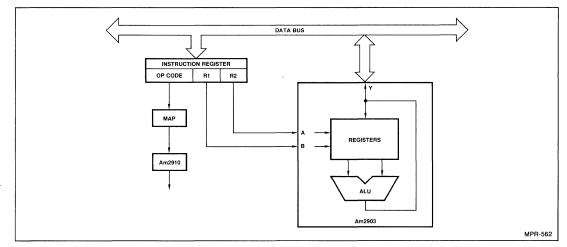

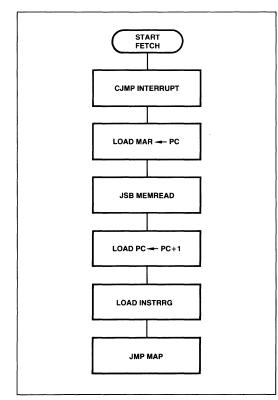

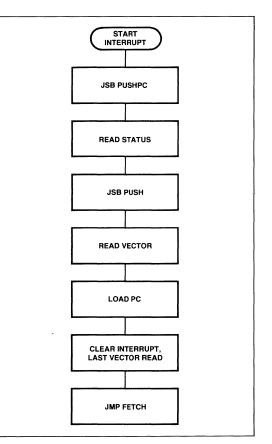

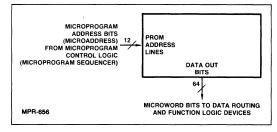

The OP-CODE (type of instruction to be executed by the computer) is loaded into the Instruction Register and the Instruction Decoder decodes it. Actually, it generates the microaddress where the first step of the execution sequence for that instruction resides in the microprogram memory. The Am2910 sequencer then generates the microaddress of the next microinstruction. The microprogram data supplies the control signals we need to control all the parts of the com-

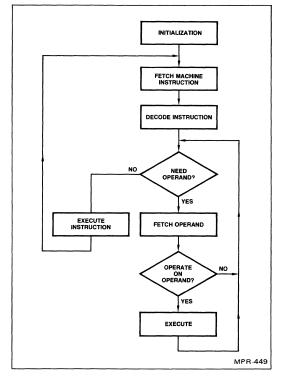

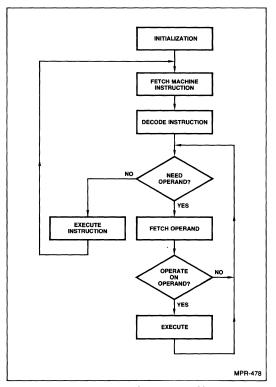

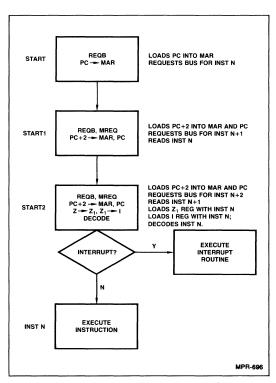

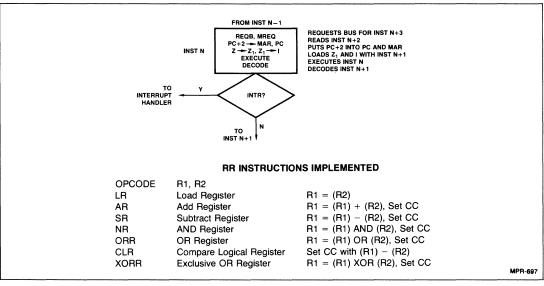

Figure 11. Computer Control Function Flow Diagram.

puter (and there are a lot of them), including the sequencer itself. When all the steps of a machine instruction are executed, the microprogram will cause the reading (fetch) of the next machine instruction from the computer main memory. Typically, the Computer Control Unit is used to fetch instructions and decode them using a PROM for mapping the op code to the initial address of the sequence of microinstructions used to execute this particular instruction. It will also fetch all of the operands needed by the machine instruction and deliver them to the ALU for processing. An example of the flow of a typical Computer Control Unit is shown in Figure 11.

Assume the OP-CODE of the machine instruction that we fetch is 8 bits wide. This allows us to execute a minimum of 256 different instructions. Assume also that an average of 6 steps are needed to execute these instructions. Even if separate microprogram memory locations are used, a depth of this microprogram memory is only 1-1/2K (K = 1024). But in that case, the sequencer can almost be replaced by a simple counter. Usually we would like to share some micro-routines among different instructions. With very little effort, we can shrink the depth of the microprogram memory of Figure 10 to less than 1/2K. Of course the sequencer will be a little more sophisticated; it will perform conditional Branch and micro-subroutine CALL's; but we still don't need the complicated addressing schemes for microprogram control as were described earlier as a part of the machine instruction set.

On the other hand, the width of our microprogram memory may be large – maybe 60 to 100 bits. This will depend on the number of control lines needed in our computer. This is of no great disadvantage since the price of PROM devices is dropping constantly. In a future chapter we will discuss techniques to reduce the depth and width of the microprogram memory to save cost.

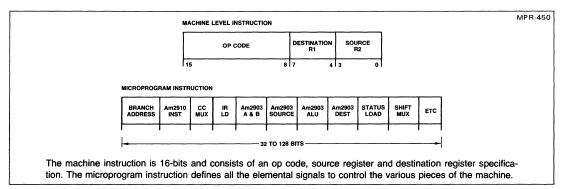

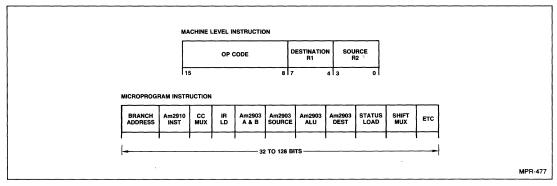

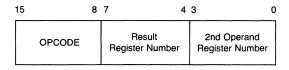

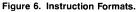

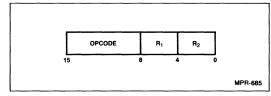

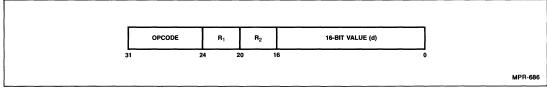

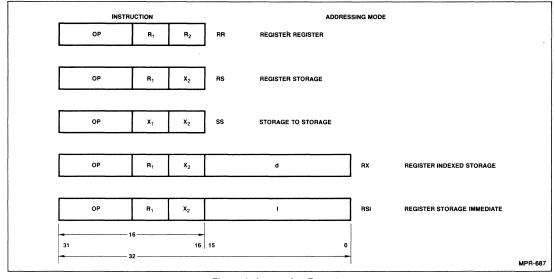

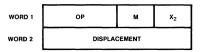

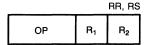

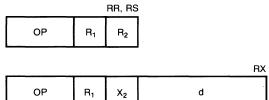

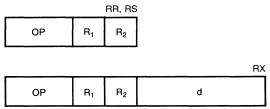

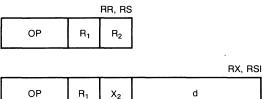

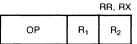

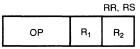

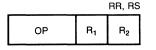

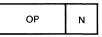

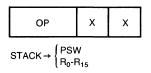

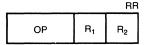

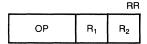

It is important to understand the distinction between machine level instructions and microprogram instructions. Figure 12 shows a typical machine instruction for a 16 bit minicomputer that has an 8-bit opcode to identify one of 256 instructions; a 4-bit source register specification to identify one of 16 source registers and a 4-bit destination register specification to identify one of 16 destination registers. The microprogram instruction of Figure 12 may contain from 32 to 128 bits in a typical design; or even more bits in a very fast, highly parallel microcoded machine. This microinstruction word usually will contain fields for the ALU source operand, ALU function, ALU destination, status load enable, shift multiplexer control, bus

Figure 12.

cycle control, etc. These fields are used to control the various devices within the machine so that its execution is as desired on each clock cycle. This is more straightforward than using combinatorial logic and yields a more organized design.

Let us now compare the depth-over-width (d/w) ratio of the computer's main memory to that of our microprogram memory.

In the Am9080A type microprocessor, the data field is 8 bits and the address field is 16 bits, allowing direct addressing of 64K locations. The ratio d/w is 8K. In some minicomputers, the data width is 16-32 bits and the addressing capability is 64-128K. The d/w ratio is about the same. In larger computers with 32-64 bit data width, we find 256-512K deep memories or even deeper ones. The d/w ratio again is 8K at least.

On the other hand, the d/w ratio in microprogram memories is seldom greater than a few tens. Even if we assume that it is 2K deep and only 64 bits wide, we arrive at a d/w ratio of only 32; usually it will be around 10. It is much easier to control a machine with a d/w ratio of 10 to 20 than to control one with d/w = 8K.

#### **ONE MORE WORD**

We have suggested a replacement of the "random logic" realization of the CCU by a micro-machine. We call this a "Microprogrammed Architecture". Perhaps the biggest advantage of this type of architecture is the ease of structuring the control sequence. We allocate a bit or a group of bits in the microprogram memory to control a certain function (e.g.: ALU source register selection, ALU function, ALU destination selection, condition selection, mAR source selection, etc., etc.) and for each microstep we write the appropriate state for these bits (LOW-HIGH) into this memory field. Later we will see that automated and sophisticated tools are available to perform this microprogram writing. One such tool is available on System 29. But, this is not the only advantage of the microprogrammed architecture. As nobody is perfect, some "bugs" may inadvertently slip into the design. In a random logic architecture, we will have to redesign and usually rebuild the whole computer. On the other hand, in a microprogrammed machine it is usually sufficient to change a couple of bits in the microprogram to rectify the problem. This is even easier if a RAM instead of a PROM is used during the development and debugging phases. Of course, we must be able to load this memory with the microprogram by some external means. Again, a powerful tool is available: AMD's System/29<sup>™</sup>.

Finally, let's face the reality: The marketing guys usually change their requirements (i.e., the instruction set) when you are 80% through your logic design. Now you have to start over from scratch. Not so! Change some microcode, perhaps very little hardware too and here you are! It is even more convenient when only additions to the existing instruction set are considered. Just add a few lines to your microprogram to comply with those new ideas! A mere few minutes using System 29 – That's flexibility! Incidentally, don't tell the marketing guys how easy it is or you will NEVER get the product out!!

#### SUMMARY

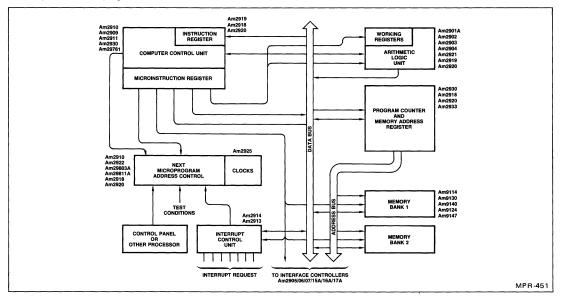

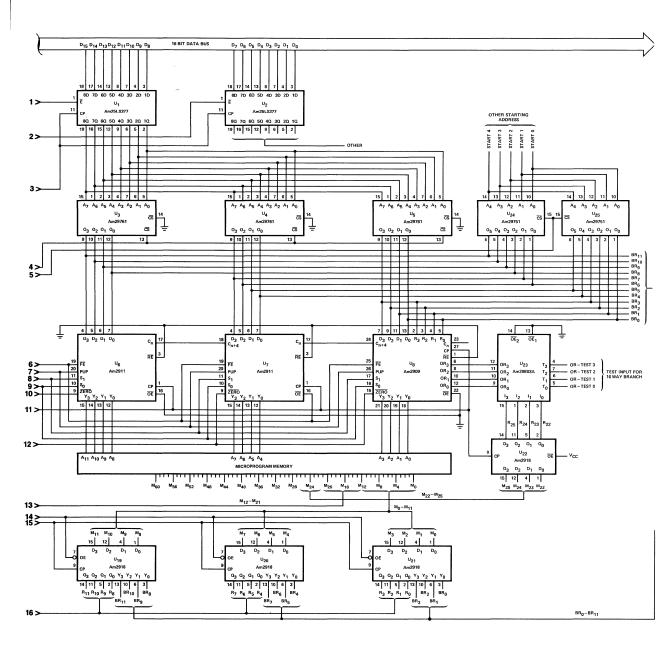

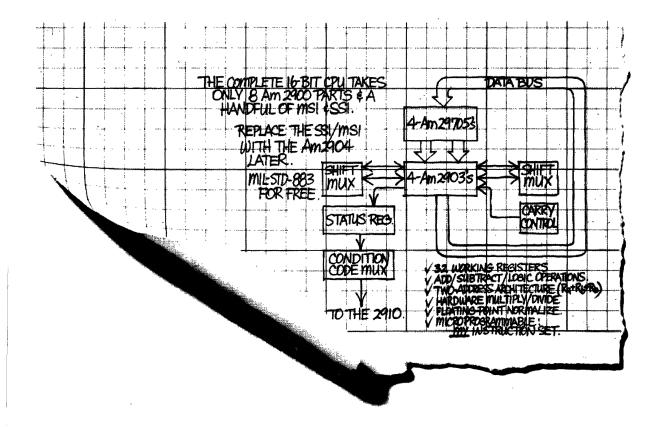

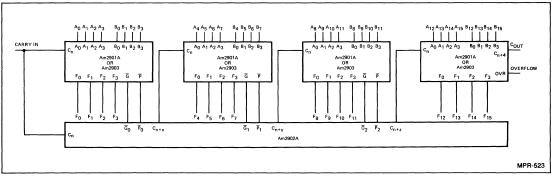

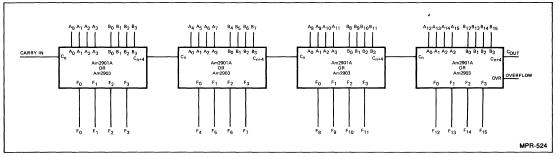

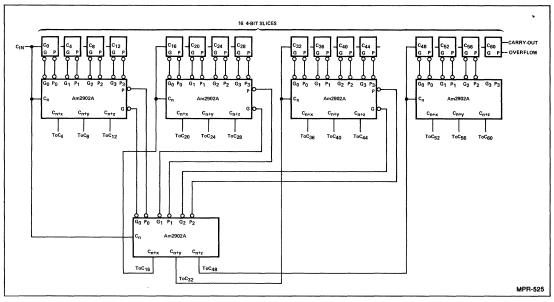

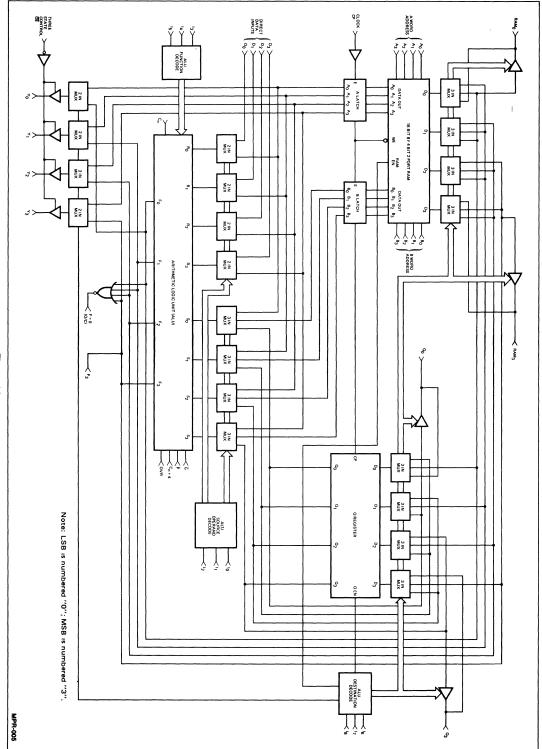

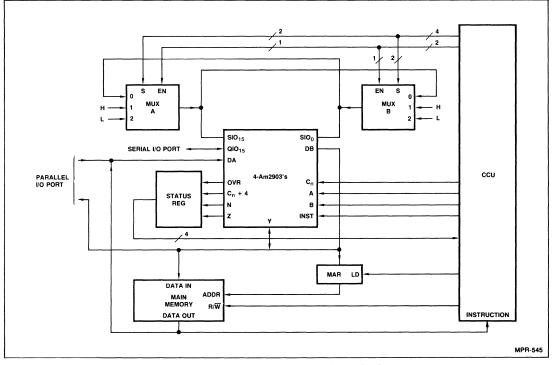

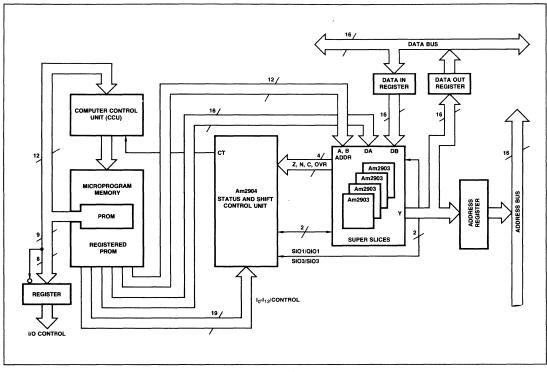

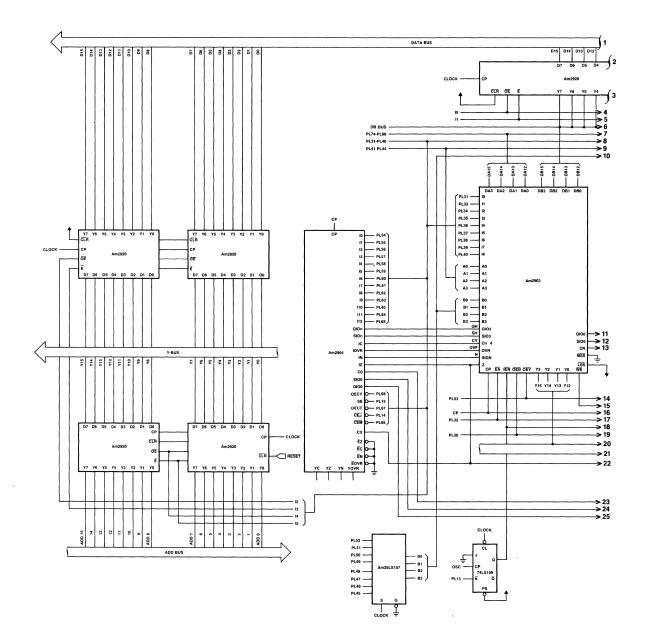

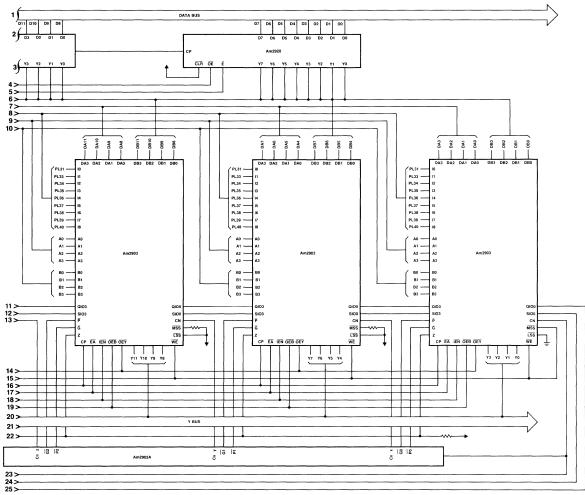

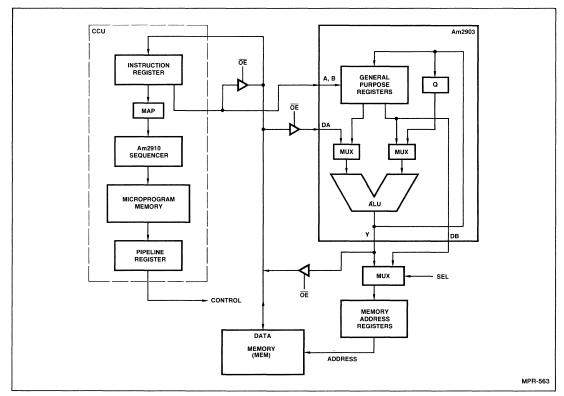

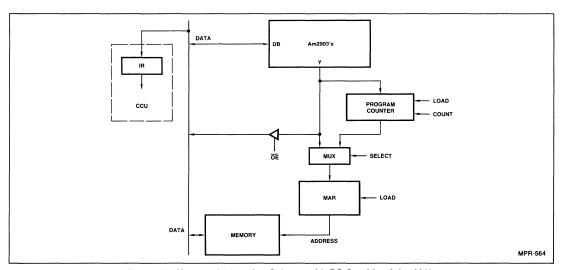

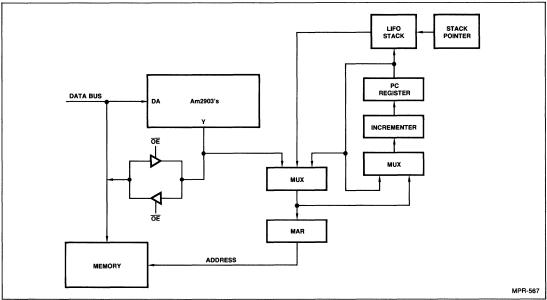

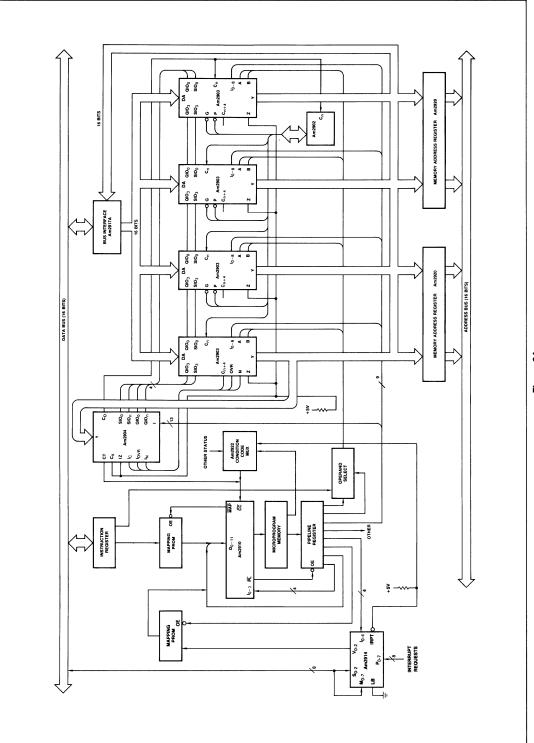

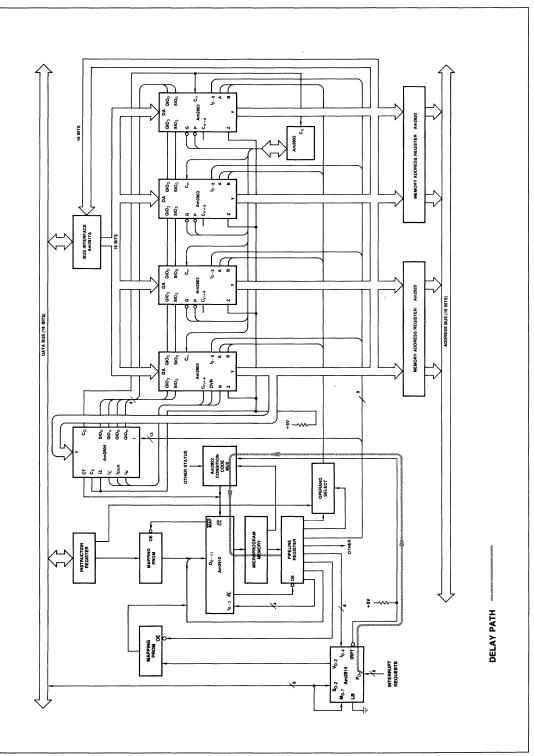

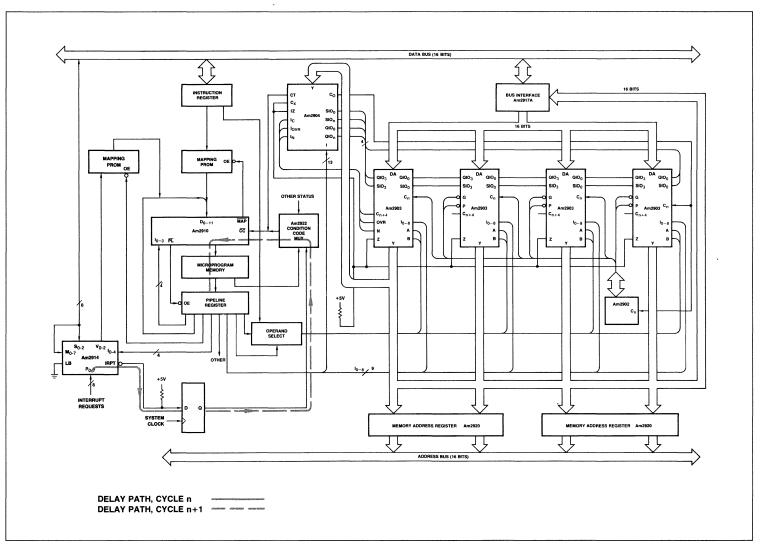

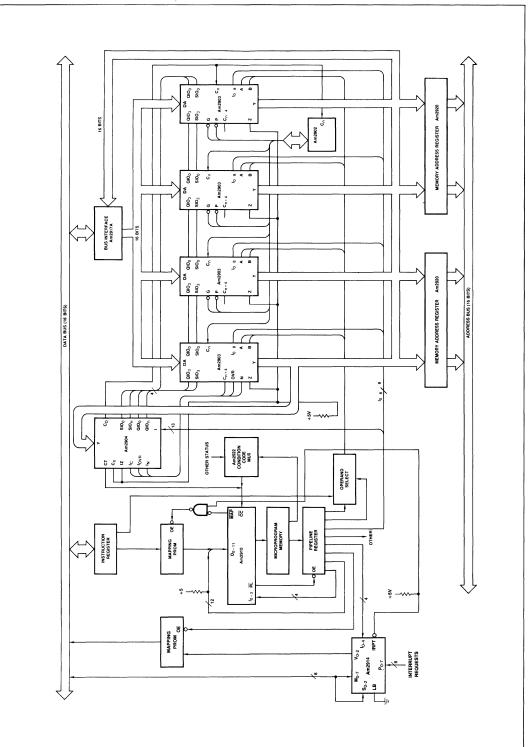

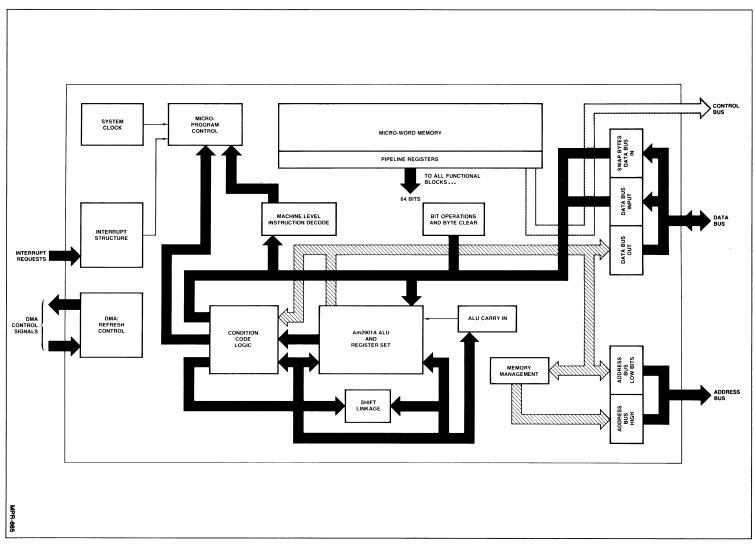

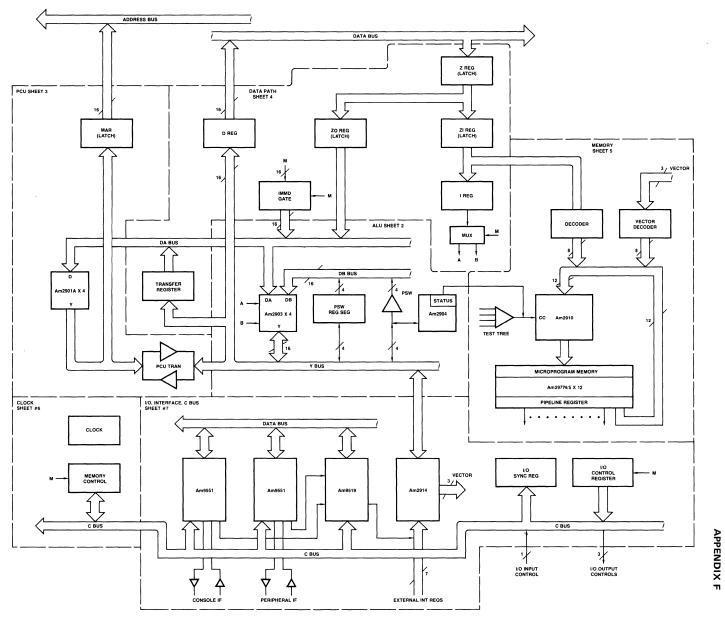

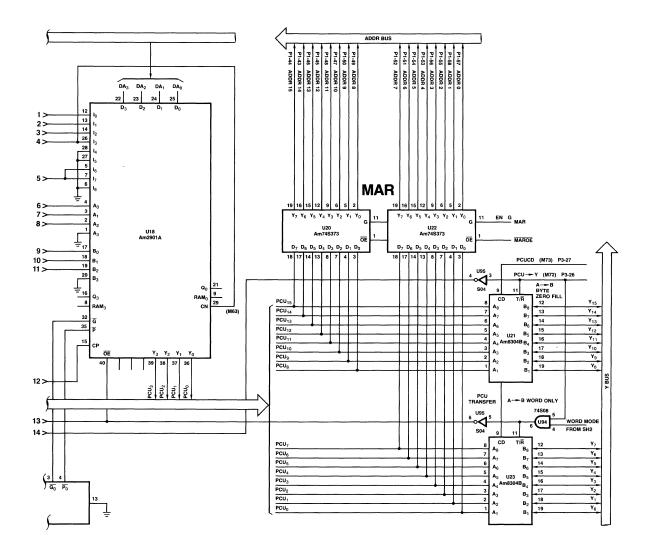

The block diagram of Figure 13 shows a typical 16-bit minicomputer architecture. Also identified on this block diagram are various Am2900 family elements that might be used in each of these blocks. Such a design might use either 4-Am2901A's or 4-Am2903's for the data path ALU. An Am2910 could be used as the microprogram sequencer for control of up to 4K words of microprogram memory. Also shown on the block diagram are the Am9130 and Am9140 MOS Static RAM's which are potential candidates for use in the computer's main memory.

The following chapters will discuss various blocks of Figure 13 in detail and give design examples for each section. Needless to say, the design engineer can appropriately tailor any design to meet his throughput requirements. Also, special algorithms can be executed by adding the appropriate hardware and microcode to the blocks described.

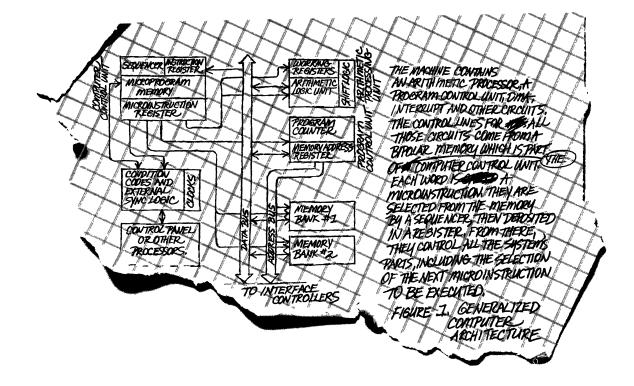

Figure 13. A Generalized Computer Architecture.

Chapter II Microprogrammed Design • . .

-

#### CHAPTER II **MICROPROGRAMMED DESIGN** INTRODUCTION

A microprogrammed machine is one in which a coherent sequence of microinstructions is used to execute various commands required by the machine. If the machine is a computer, each sequence of microinstructions can be made to execute a machine instruction. All of the little elemental tasks performed by the machine in executing the machine instruction are called microinstructions. The storage area for these microinstructions is usually called the microprogram memory. This technique was identified by Wilkes in the 1950's as a structured approach to the random control logic in a computer.

A microinstruction usually has two primary parts. These are: (1) the definition and control of all elemental microoperations to be carried out and (2) the definition and control of the address of the next microinstruction to be executed.

The definition of the various micro-operations to be carried out usually includes such things as ALU source operand selection, ALU function, ALU destination, carry control, shift control, interrupt control, data-in and data-out control and so forth. The definition of the next microinstruction function usually includes identifying the source selection of the next microinstruction address, and in some cases, supplying the actual value of that microinstruction address.

Microprogrammed machines are usually distinguished from non-microprogrammed machines in the following manner. Older, non-microprogrammed machines implemented the control function by using combinations of gates and flip-flops connected in a somewhat random fashion in order to generate the required timing and control signals for the machine. Microprogrammed machines, on the other hand, are normally considered highly ordered and more organized with regard to the control function field. In its simplest definition, a microprogram control unit consists of the microprogram memory and the structure required to determine the address of the next microinstruction.

Microprogramming is normally selected by the design engineer as a control technique for finite state machines because it improves flexibility, performance, and LSI utilization. Several additional key features of microprogrammed designs are listed below:

- More structured organization

- Diagnostics can be implemented easily

- Design changes are simple

- Field updates are easy

- Adaptations are straightforward

- · System definition can be expanded to include new features

- Documentation and Service are easier

- Design aids are available

- Cost and design time are reduced

#### THE MICROPROGRAM MEMORY

The microprogram memory is simply an N word by M bit memory used to hold the various microinstructions. For an N word memory, the address locations are usually defined as location 0 through N-1. For example, a 256-word microprogram memory will have address locations 0 through 255. Each word of the microprogram memory consists of M bits. These M bits are usually broken into various field definitions and the fields can consist of various numbers of bits. It is the definition of the various fields of a microprogram word that is usually referred to as FORMATTING.

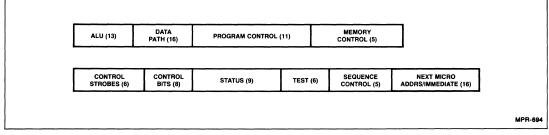

An example of how microinstruction fields are defined in a typical machine microprogram memory word is as follows:

- Field 1 General purpose

- Field 2 Branch address

- Field 3 Next microinstruction address control Field 4 – Condition code multiplexer control

- Field 5 Interrupt control

- Field 6 Fast clock/slow clock select

- Field 7 Carry control

- Field 8 ALU source operand control

- Field 9 ALU function control

- Field 10 ALU destination control

- Field 11 Shift multiplexer control

- Field 12 etc.

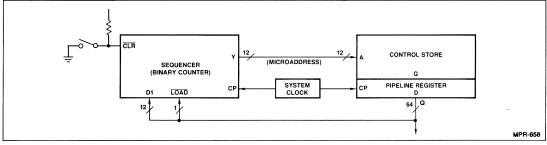

#### EXECUTING MICROINSTRUCTONS

Once the microprogram format has been defined, it is necessary to execute sequences of these microinstructions if the machine is to perform any real function. In its simplest form, all that is required to sequence through a series of microinstructions is a microprogram address counter. The microprogram address counter simply increments by one on each clock cycle to select the address of the next microinstruction. For example, if the microprogram address counter contains address 23, the next clock cycle will increment the counter and it will select address 24. The counter will continue to increment on each clock cycle thereby selecting address 25, address 26, address 27, and so forth. If this were the only control available, the machine would not be very flexible and it would be able to execute only a fixed pattern of microinstructions.

The technique of continuing from one microinstruction to the next sequential microinstruction is usually referred to as CON-TINUE. Thus, in microprogram control definition, we will use the CONTINUE (CONT) statement to mean simply incrementing to the next microinstruction.

#### MICROPROGRAM JUMPING

If the microprogram control unit is to have the ability to select other than the next microinstruction, the control unit must be able to load a JUMP address. The load control of a counter can be a single bit field within the microprogram word format. Let us call this one-bit field the microprogram address counter load enable bit. When this bit is at logic 0, a load will be inhibited and when this bit is a logic 1, a load will be enabled. If the load is enabled, the JUMP address contained within the microprogram memory will be parallel loaded into the microprogram address counter. This results in the ability to perform an N-way branch. For example, if the branch address field is eight bits wide, a JUMP to any address in the memory space from word 0 through word 255 can be performed.

This simple branching control feature allows a microprogram memory controller to execute sequential microinstructions or perform a JUMP (JMP) to any address either before or after the address currently contained in the microprogram address counter.

#### CONDITIONAL JUMPING

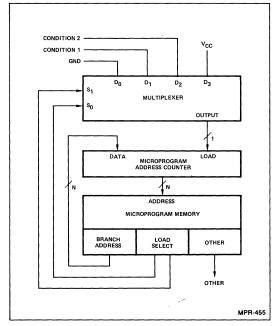

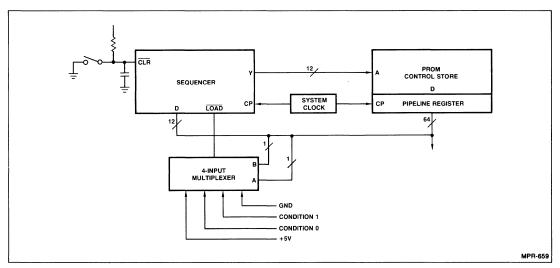

While the JUMP instruction has added some flexibility to the sequencing of microprogram instructions, the controller still lacks any decision-making capability. This decision-making capability is provided by the CONDITIONAL JUMP (COND JMP) instruction. Figure 1 shows a functional block diagram of a microprogram memory/address controller providing the capability to jump on either of two different conditions. In this example, the load select control is a two-bit field used to control a

Figure 1. A Two-Bit Control Field Can be Used to Select CONTINUE, BRANCH, or CONDITIONAL BRANCH.

four-input multiplexer. When the two-bit field is equivalent to binary zero, the multiplexer selects the zero input which forces the load control inactive. Thus, the CONTINUE microprogram control instruction is executed. When the two-bit load select field contains binary one, the D1 input of the multiplexer is selected. Now, the load control is a function of the Condition 1 input. If Condition 1 is logic 0, the microprogram address counter increments and if Condition 1 is logic 1, the jump address will be parallel loaded in the next clock cycle. This operation is defined as a CONDITIONAL JUMP. If the load select input contains binary 2, the D2 input is selected and the same conditional function is performed with respect to the Condition 2 input. If the load select field contains binary 3, the D<sub>3</sub> input of the multiplexer is selected. Since the D<sub>2</sub> input is tied to logic HIGH, this forces the microprogram address counter to the load mode independent of anything else. Thus, the jump address is loaded into the microprogram address counter on the next clock cycle and an UNCONDITIONAL JUMP is executed. This load select control function definition is shown in Table 1.

TABLE 1. LOAD SELECT CONTROL FUNCTION.

| S <sub>1</sub> S <sub>0</sub> | Function              |

|-------------------------------|-----------------------|

| 00                            | Continue              |

| 0 1                           | Jump Condition 1 True |

| 10                            | Jump Condition 2 True |

| 11                            | Jump Unconditional    |

## OVERLAPPING THE MICROPROGRAM INSTRUCTION FETCH

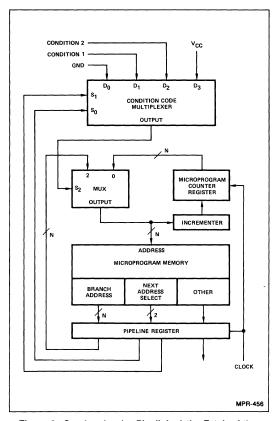

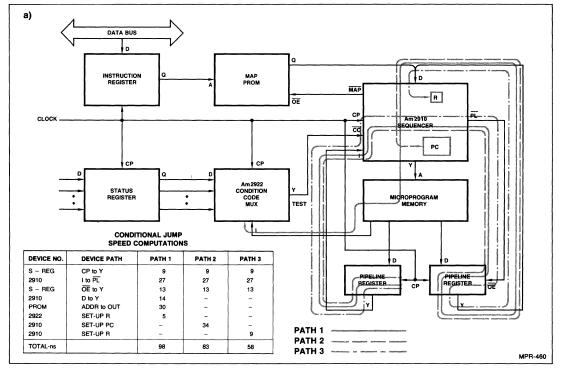

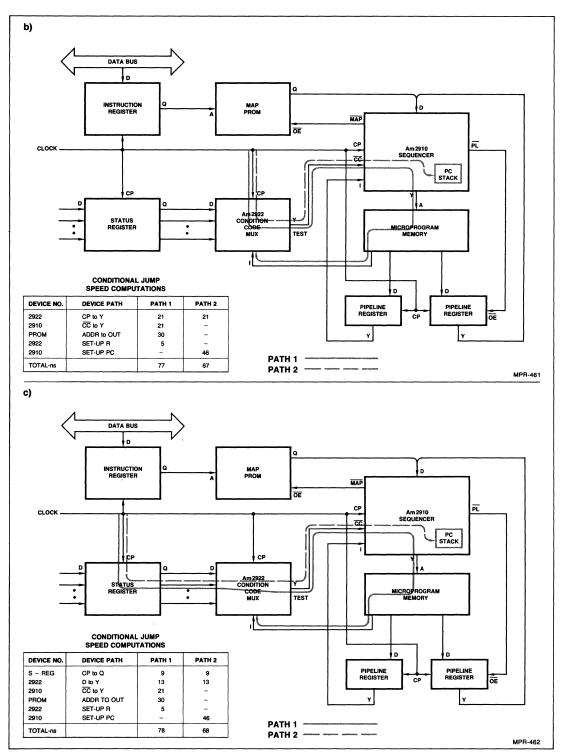

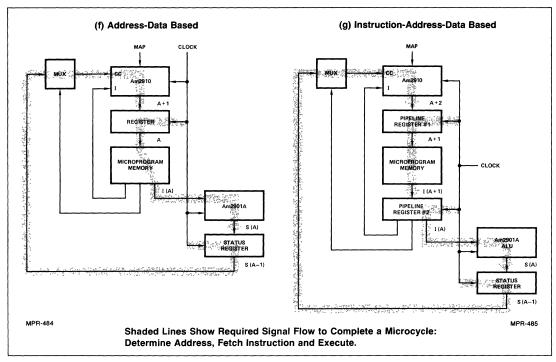

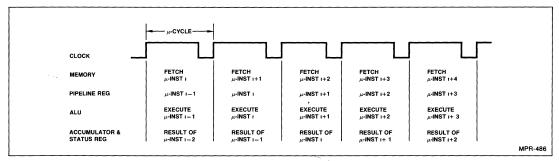

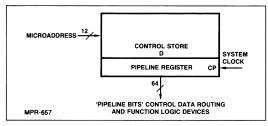

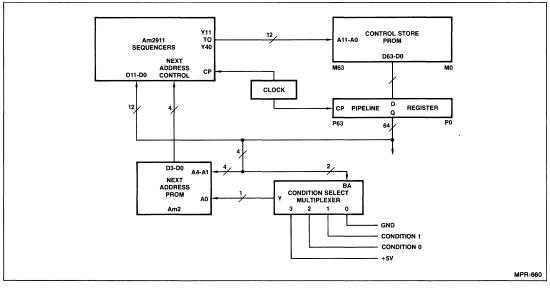

Now that a few basic microprogram address control instructions have been defined, let us examine the control instructions used in a microprogram control unit featuring the overlap fetching of the next microinstruction. This technique is also known as "pipelining". The block diagram for such a microprogram control unit is shown in Figure 2. The key difference when compared with previous microprogrammed architectures is the existence of the "pipeline register" at the output of the microprogram memory. By definition, the pipeline register (or microword register) contains the microinstruction currently being executed by the machine. Simultaneously, while this microinstruction is being executed, the address of the next microinstruction is applied to the microprogram memory and the contents of that memory word are being fetched and set-up at the inputs to the pipeline register. This technique of pipelining can be used to improve the performance of the microprogram control unit. This results because the contents of the microprogram memory word required for the next cycle are being fetched on an overlapping basis with the actual execution of the current microprogram word. It should be realized that when the pipeline approach is used, the design engineer must be aware of the fact that some registers contain the results of the previous microinstruction executed, some registers contain the current microinstruction being executed, and some registers contain data for the next microinstruction to be executed.

Figure 2. Overlapping (or Pipelining) the Fetch of the Next Microinstruction.

Let us now compare the block diagram of Figure 2 with that shown in Figure 1. The major difference, of course, is the addition of the pipeline register at the output of the microprogram control memory. Also, notice the addition of the address multiplexer at the source of the microprogram memory address. This address multiplexer is used to select the microprogram counter register or the pipeline register as the source of the next address for the microprogram memory. The condition code multiplexer is used to control the address multiplexer in this address selection. By placing an incrementer at the output of the address multiplexer, is is possible to always generate the current microprogram address "plus one" at the input of the micropprogram counter register.

In Figure 1, the microprogram address counter was described as a counter and could be a device such as the Am25LS161 counter. In the implementation as shown in Figure 2, the Am25LS161 counter is not appropriate. Instead, an incrementer and register are used to give the equivalent effect of a counter.

The key difference between using a true binary counter and the incrementer register described here is as follows. When the jump address from the pipeline register is selected by the multiplexer, the incrementer will combinatorially prepare that address plus one for entry into the microprogram counter register. This entry will occur on the LOW-to-HIGH transition of the clock. Thus, the microprogram counter register can always be made to contain address plus one, independent of the selection of the next microinstruction address. When the address multiplexer is switched so that the microprogram counter register is selected as the source of the microprogram memory address, the incrementer will again set-up address plus one for entry into the microprogram counter register. Thus, when the address multiplexer selects the microprogram counter register, the address multiplexer, incrementer and microprogram counter register appear to operate as a normal binary counter.

The condition code multiplexer  $S_0S_1$  operates in exactly the same fashion as described for the condition code multiplexer of Figure 1. That is, binary zero in the pipeline register (the current microinstruction being executed) forces an unconditional selection of the microprogram register via  $D_0$ . Binary one or binary two in the next address select control bits of the pipeline register cause a conditional selection at the address multiplexer via  $D_1$  or  $D_2$ . Thus, a CONDITIONAL JUMP can be executed. Binary three in the next address select portion of the pipeline register causes an UNCONDITIONAL JUMP instruction to be executed via  $D_3$ .

When the overall machine timing is studied, it will be observed that the key difference between overlap fetching and nonoverlap fetching involves the propagation delay of the microprogram memory. In the non-pipelined architecture, the microprogram memory propagation delay must be added to the propagation delay of all the other elements of the machine. In the overlap fetch architecture, the propagation delay associated with the next microprogram memory address fetch is a separate loop independent of the other portion of the machine.

#### SUBROUTINING IN MICROPROGRAMMING CONTROL

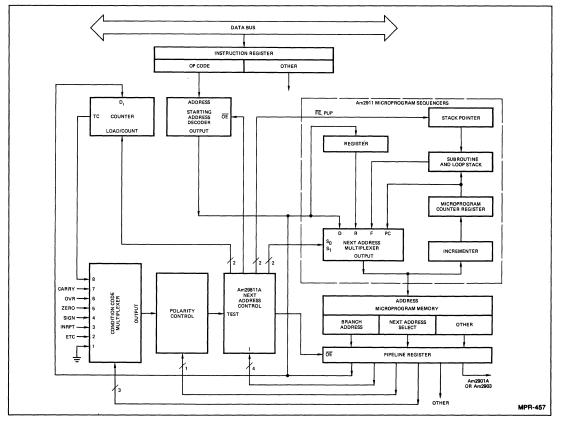

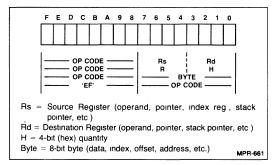

Thus far, we have examined the CONTINUE instruction as well as the CONDITIONAL and UNCONDITIONAL JUMP instructions for overlap fetch. Just as in the programming of minicomputers and microcomputers, the advantages of SUBROUTIN-ING can be realized in microprogramming. The idea here, of course, is that the same block of microcode (or even a single microinstruction) can be shared by several microinstruction sequences. This results in an overall reduction in the total number of microprogram memory words required by the design. If we are to jump to a subroutine, what is required is the ability to store an address to which the subroutine should return when it has completed its execution. Examining the block diagram of Figure 3, we see the addition of a subroutine and loop (push/pop) stack (also called the file) and its associated stack pointer. The control signals required by the stack are an enable stack signal (FILE ENABLE = FE) which will be used to tell the file whenever we wish to perform a push or a pop, and a push/pop control (PUP) used to control the direction of the stack pointer (push or pop).

In this architecture, the stack pointer always points to the address of the last microinstruction written on the stack. This allows the "next address multiplexer" to read the stack at any time via port F. When this selection is performed, the last word written on the stack will be the word applied to the microprogram memory. The condition code multiplexer of the previous example has also been replaced by a next address control unit. This next address control unit (Am29811A) can execute 16 different next address control functions where most of these functions are conditional. Thus, the device has four instruction inputs as well as one condition code test input which is connected to the condition code multiplexer. Note also that the next address control field of the microprogram word has been expanded to a four-bit field. Outputs from the Am29811A next address control block are used to control the stack pointer and the next address multiplexer of the Am2911. In addition, the device has outputs to control the three-state enable of the pipeline register and the three-state enable of the starting address decode PROM. Also, the architecture has a counter that can be used as a loop-counter or event counter.

The 16 instructions associated with the Am29811A are listed in Table 2. As is easily seen by referring to Table 2, three of the instructions in this set are associated with subroutining in microprogram memory. The first instruction of this set, is a simple conditional JUMP-TO-SUBROUTINE where the source of the subroutine address is in the pipeline register. The RETURN-FROM-SUBROUTINE instruction is also conditional and is used to return to the next microinstruction following the JUMP-TO-SUBROUTINE instruction. There is also a conditional JUMP-TO-SUBROUTINE instruction. There is also a conditional JUMP-TO-ONE-OF-TWO-SUBROUTINE, where the subroutine address is either in the PIPELINE register or in the internal REG-ISTER in the Am2911. This instruction will be explained in more detail later.

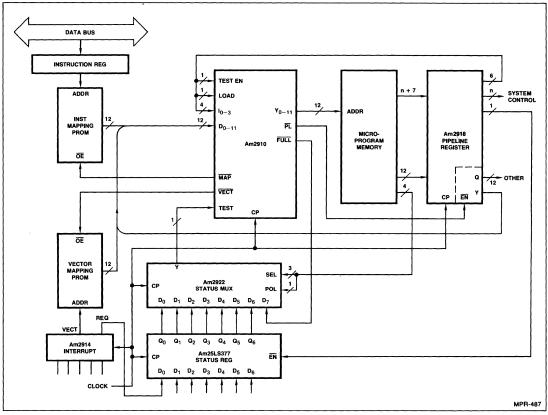

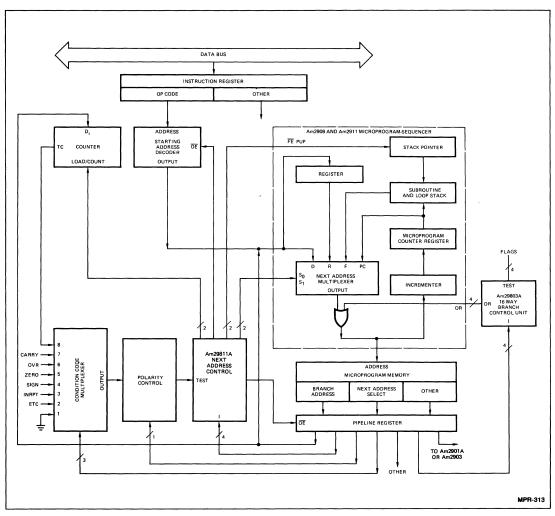

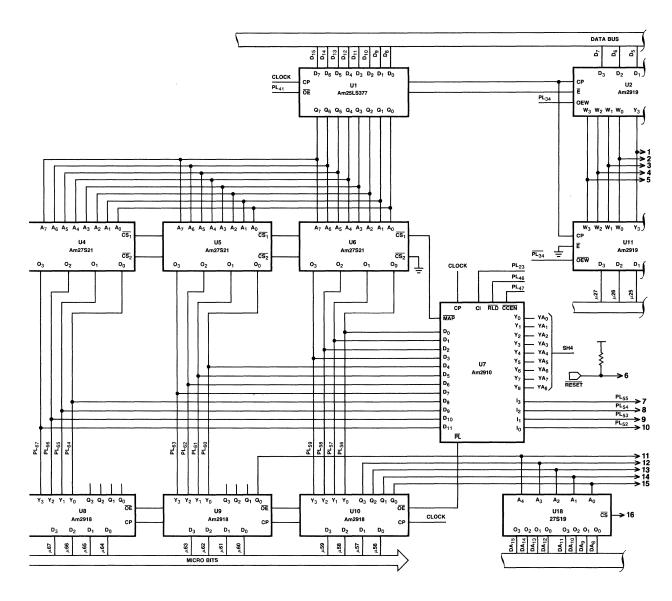

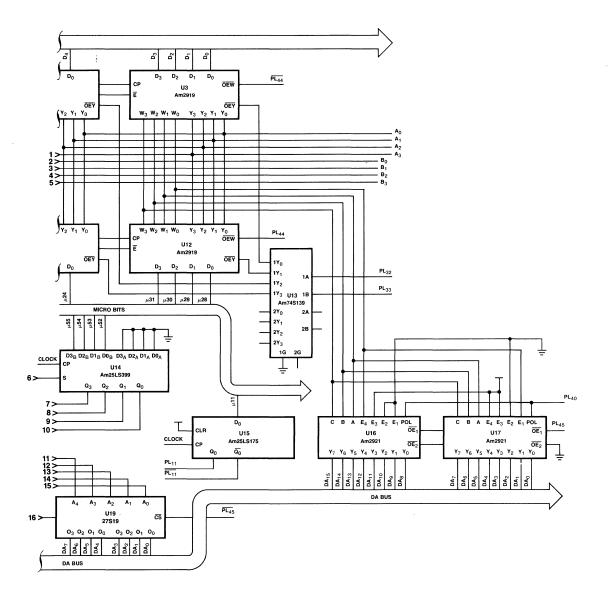

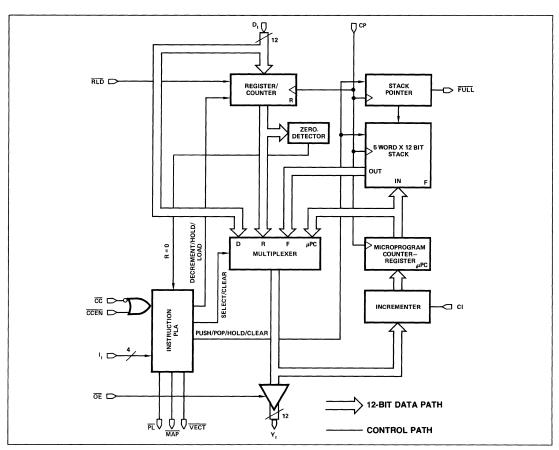

#### TYPICAL COMPUTER CONTROL UNIT ARCHITECTURE USING THE Am2911 AND Am29811A

The microprogram memory control unit block diagram of Figure 3 is easily implemented using the Am2911 and Am29811A. This architecture provides a structured state machine design capable of executing many highly sophisticated next address control instructions. The Am2911 contains a next address multiplexer that provides four different inputs from which the address of the next microinstruction can be selected. These are the direct input (D), the register input (R), the program counter (PC), and the file (F). The starting address decoder (mapping PROM) output and the pipeline register output are connected together at the D input to the Am2911 and are operated in the three-state mode.

The architecture of Figure 3 shows an instruction register capable of being loaded with a machine instruction word from the data bus. The op code portion of the instruction is decoded using a mapping PROM to arrive at a starting address for the

|          |                 |        | INPUTS                   |               | OUTPUTS             |      |         |       |      |

|----------|-----------------|--------|--------------------------|---------------|---------------------|------|---------|-------|------|

| MNEMONIC | INSTRU<br>I3 I2 | ICTION | FUNCTION                 | TEST<br>INPUT | NEXT ADDR<br>SOURCE | FILE | COUNTER | MAP-E | PL-E |

| JZ       | LL              | LL     | JUMP ZERO                | x             | D                   | HOLD | LL      | н     | L    |

| CJS      | LL              | LH     | COND JSB PL              | L             | PC                  | HOLD | HOLD    | н     | L    |

|          | {               |        |                          | н             | D                   | PUSH | HOLD    | н     | L    |

| JMAP     | LL              | HL     | JUMP MAP                 | x             | D                   | HOLD | HOLD    | L     | н    |

| CJP      | LL              | нн     | COND JUMP PL             | L             | PC                  | HOLD | HOLD    | н     | L    |

|          |                 |        |                          | н             | D                   | HOLD | HOLD    | н     | L    |

| PUSH     | LH              | LL     | PUSH/COND LD CNTR        | L             | PC                  | PUSH | HOLD    | н     | L    |

|          |                 |        |                          | н             | PC                  | PUSH | LOAD    | н     | L    |

| JSRP     | LH              | LH     | COND JSB R/PL            | L             | R                   | PUSH | HOLD    | н     | L,   |

|          | 1               |        |                          | н             | D                   | PUSH | HOLD    | н     | L    |

| CJV      | LH              | HL     | COND JUMP VECTOR         | L             | PC                  | HOLD | HOLD    | н     | н    |

|          |                 |        |                          | н             | D                   | HOLD | HOLD    | н     | н    |

| JRP      | LH              | нн     | COND JUMP R/PL           | L             | R                   | HOLD | HOLD    | н     | L    |

|          | 1               |        |                          | н             | D                   | HOLD | HOLD    | н     | L    |

| RFCT     | HL              | LL     | REPEAT LOOP, CNTR ≠ 0    | L             | F                   | HOLD | DEC     | н     | L    |

|          |                 |        |                          | н             | PC                  | POP  | HOLD    | н     | L    |

| RPCT     | HL              | LH     | REPEAT PL, CNTR $\neq 0$ | L             | D                   | HOLD | DEC     | н     | L    |

|          |                 |        |                          | н             | PC                  | HOLD | HOLD    | н     | L    |

| CRTN     | HL              | HL     | COND RTN                 | L             | PC                  | HOLD | HOLD    | н     | L    |

|          |                 |        |                          | н             | F                   | POP  | HOLD    | н     | L    |

| CJPP     | HL              | нн     | COND JUMP PL & POP       | L             | PC                  | HOLD | HOLD    | н     | L    |

|          |                 |        |                          | н             | D                   | POP  | HOLD    | н     | L    |

| LDCT     | нн              | LL     | LOAD CNTR & CONTINUE     | x             | PC                  | HOLD | LOAD    | н     | L    |

| LOOP     | нн              | LH     | TEST END LOOP            | L             | F                   | HOLD | HOLD    | н     | L    |

|          |                 |        | 1                        | н             | PC                  | POP  | HOLD    | н     | L    |

| CONT     | нн              | HL     | CONTINUE                 | x             | PC                  | HOLD | HOLD    | н     | L    |

| JP       | нн              | нн     | JUMP PL                  | x             | D                   | HOLD | HOLD    | н     | L    |

TABLE 2. FUNCTIONAL DESCRIPTION OF Am29811A INSTRUCTION SET.

Figure 3. A Typical Computer Control Unit Using the Am2911 and Am29811A.

| TABLE 3. PIN FUNCTIONS | TA | BLE | З. | PIN | FUN | CTI | ONS. |

|------------------------|----|-----|----|-----|-----|-----|------|

|------------------------|----|-----|----|-----|-----|-----|------|

| Abbreviation | Name                       | Function                                                                                                                               |

|--------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| DI           | Direct Input Bit i         | Direct input to register/counter and multiplexer. Do is LSB                                                                            |

| 4            | Instruction Bit i          | Selects one-of-sixteen instructions for the Am2910                                                                                     |

| CC           | Condition Code             | Used as test criterion. Pass test is a LOW on CC.                                                                                      |

| CCEN         | Condition Code Enable      | Whenever the signal is HIGH, $\overline{\text{CC}}$ is ignored and the part operates as though $\overline{\text{CC}}$ were true (LOW). |

| CI           | Carry-In                   | Low order carry input to incrementer for microprogram counter                                                                          |

| RLD          | Register Load              | When LOW forces loading of register/counter regardless of<br>instruction or condition                                                  |

| ŌĒ           | Output Enable              | Three-state control of Y <sub>1</sub> outputs                                                                                          |

| CP           | Clock Pulse                | Triggers all internal state changes at LOW-to-HIGH edge                                                                                |

| Vcc          | +5 Volts                   |                                                                                                                                        |

| GND          | Ground                     |                                                                                                                                        |

| Yi           | Microprogram Address Bit i | Address to microprogram memory. Yo is LSB, Y11 is MSB                                                                                  |

| FULL         | Full                       | Indicates that five items are on the stack                                                                                             |

| PL           | Pipeline Address Enable    | Can select #1 source (usually Pipeline Register) as direct<br>input source                                                             |

| MAP          | Map Address Enable         | Can select #2 source (usually Mapping PROM or PLA) as<br>direct input source                                                           |

| VECT         | Vector Address Enable      | Can select #3 source (for example, Interrupt Starting Address) as direct input source                                                  |

microinstruction sequence required to execute the machine instruction. When the microprogram memory address is to be the first microinstruction of the machine instruction sequence, the Am29811A next address control unit selects the multiplexer D input and enables the three-state output from the mapping PROM. When the current microinstruction being executed is selecting the next microinstruction address as a JUMP function, the JUMP address will be available at the multiplexer D input. This is accomplished by having the Am29811A select the next address multiplexer D input and also enabling the three-state output of the pipeline register branch address field. The register enable input to the Am2911 is connected to ground so that this register will always load the value at the Am2911 D input. The value at D is clocked into the Am2911's register (R) at the end of the current microcycle, which makes the D value of this microcycle available as the R value of the next microcycle. Thus, by using the branch address field of two sequential microinstructions, a conditional JUMP-TO-ONE-OF-TWO-SUBROUTINES or a conditional JUMP-TO-ONE-OF-TWO-BRANCH-ADDRESSES can be executed by either selecting the D input or the R input of the next address multiplexer.

When sequencing through continuous microinstructions in microprogram memory, the program counter in the Am2911 is used. Here, the Am29811A simply selects the PC input of the next address multiplexer. In addition, most of these instructions enable the three-state outputs of the pipeline register associated with the branch address field, which allows the register within the Am2911 to be loaded.

The 4 x 4 stack in the Am2911 is used for looping and subroutining in microprogram operations. Up to four levels of subroutines or loops can be nested. Also, loops and subroutines can be intermixed as long as the four-word depth of the stack is not exceeded.

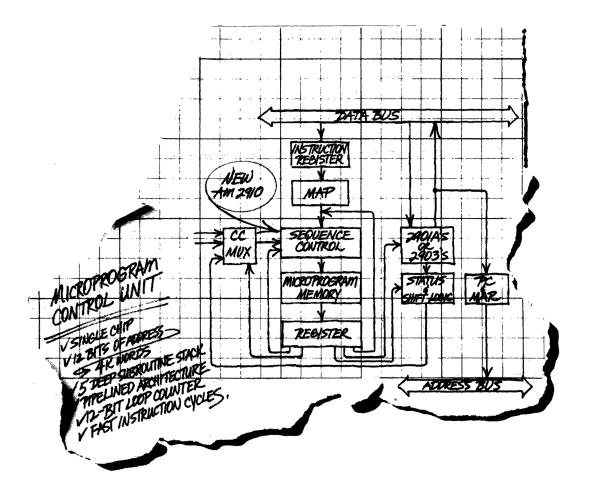

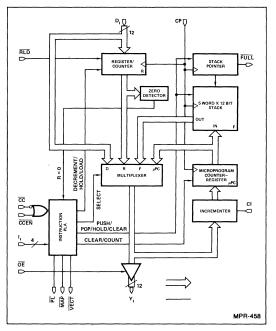

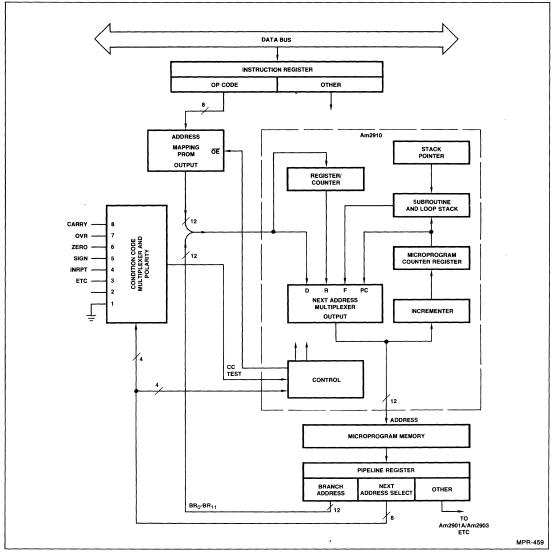

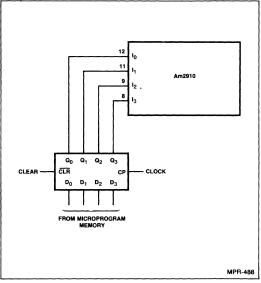

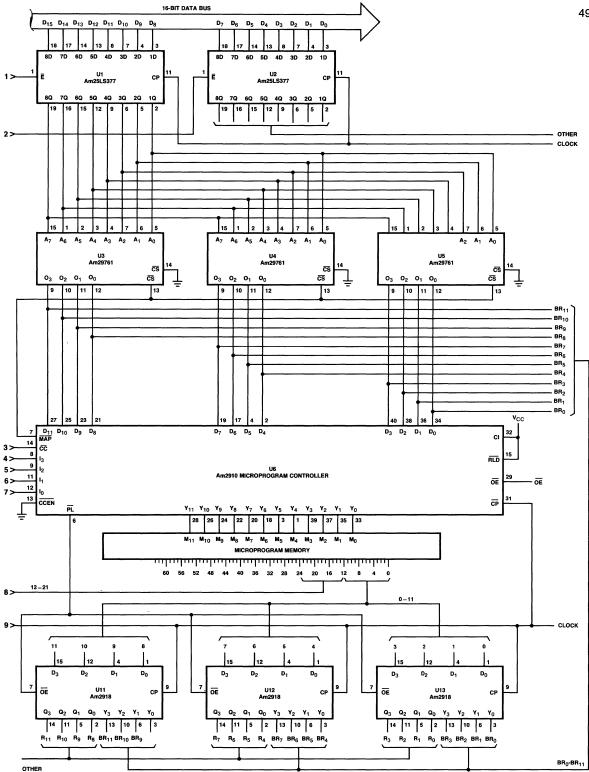

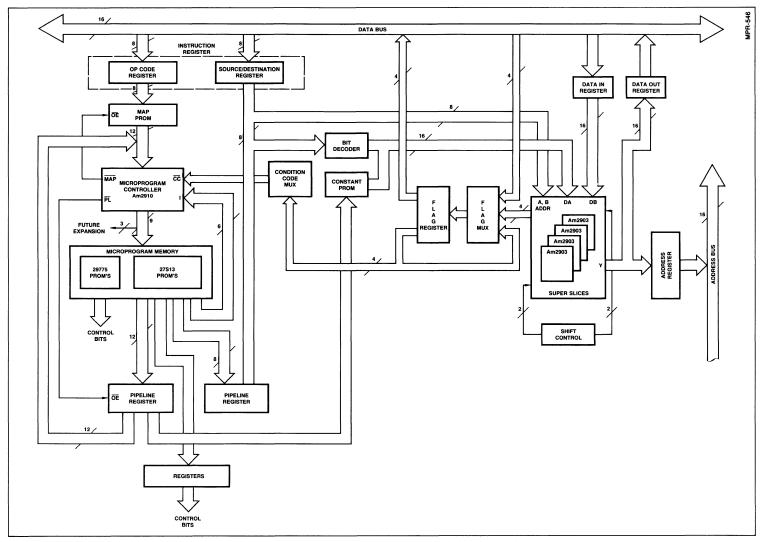

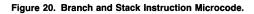

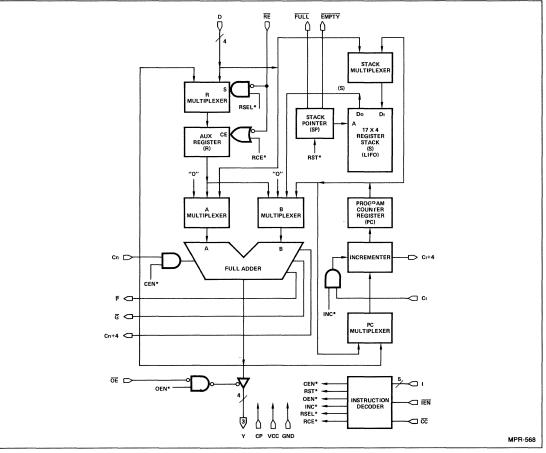

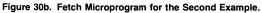

#### **ARCHITECTURE OF THE Am2910**

The Am2910 is a bipolar microprogram controller intended for use in high-speed microprocessor applications. It allows addressing of up to 4K words of microprogram. A block diagram is shown in Figure 4. The controller contains a four-input multiplexer that is used to select either the register/counter, direct input, microprogram counter, or stack as the source of the next microinstruction address.

The register/counter consists of 12 D-type, edge-triggered flipflops, with a common clock enable. When its load control,  $\overline{RLD}$ , is LOW, new data is loaded on a positive clock transition. A few instructions include load; in most systems, these instructions will be sufficient, simplifying the microcode. The output of the register/counter is available to the multiplexer as a source for the next microinstruction address. The direct input furnishes a source of data for loading the register/counter.

Figure 4. Am2910 Block Diagram.

The Am2910 contains a microprogram counter ( $\mu$ PC) that is composed of a 12-bit incrementer followed by a 12-bit register. The  $\mu$ PC can be used in either of two ways When the carry-in to the incrementer is HIGH, the microprogram register is loaded on the next clock cycle with the current Y output word plus one (Y+1  $\rightarrow \mu$ PC). Sequential microinstructions are thus executed. When the carry-in is LOW, the incrementer passes the Y output word unmodified so that  $\mu$ PC is reloaded with the same Y word on the next clock cycle (Y  $\rightarrow \mu$ PC). The same microinstruction is thus executed any number of times.

The third source for the multiplexer is the direct (D) inputs. This source is used for branching.

The fourth source available at the multiplexer input is a 5-word by 12-bit stack (file). The stack is used to provide return address linkage when executing microsubroutines or loops. The stack contains a build-in stack pointer (SP) which always points to the last file word written. This allows stack reference operations (looping) to be performed without a pop. The stack pointer operates as an up/down counter. During microinstructions 2, 4 and 5, the PUSH operation is performed. This causes the stack pointer to increment and the file to be written with the required return linkage. On the cycle following the PUSH, the return data is at the new location pointed to by the stack pointer.

During six other microinstructions, a POP operation occurs. This places the information at the top of the stack onto the Y outputs. The stack pointer decrements at the next rising clock edge following a POP, effectively removing old information from the top of the stack.

The stack pointer linkage is such that any sequence of pushes, pops or stack references can be achieved. At RESET (Instruction 0), the depth of nesting becomes zero. For each PUSH, the nesting depth increases by one; for each POP, the depth decreases by one. The depth can grow to five. After a depth of five is reached, FULL goes LOW. Any further PUSHes onto a full stack overwrites information at the top of the stack, but leaves the stack pointer unchanged. This operation will usually destroy useful information and is normally avoided. A POP from an empty stack places non-meaningful data on the Y outputs, but is otherwise safe. The stack pointer remains at zero whenever a POP is attempted from a stack already empty. The register/counter is operated during three microinstructions (8, 9, 15) as a 12-bit down counter, with result = zero available as a microinstruction branch test criterion. This provides efficient iteration of microinstructions. The register/counter is arranged such that if it is preloaded with a number N and then used as a loop termination counter, the sequence will be executed exactly N+1 times. During instruction 15, a three-way branch under combined control of the loop counter and the condition code is available.

The device provides three-state Y outputs. These can be particularly useful in designs requiring automatic checkout of the processor. The microprogram controller outputs can be forced into the high-impedance state, and pre-programmed sequences of microinstructions can be executed via external access to the address lines.

#### OPERATION

Table 4 shows the result of each instruction in controlling the multiplexer which determines the Y outputs, and in controlling the three enable signals PL, MAP and VECT. The effect on the  $\mu$ PC, the register/counter, and the stack after the next positive-going clock edge is also shown. The multiplexer determines which internal source drives the Y outputs. The value loaded into  $\mu$ PC is either identical to the Y output, or else one greater, as determined by CI. For each instruction, one and only one of the three outputs PL, MAP and VECT is LOW. If these outputs control three-state enables for the primary source of microprogram jumps (usually part of a pipeline register), a PROM which maps the instruction to a microinstruction starting location, and an optional third source (often a vector from a DMA or interrupt source), respectively, the three-state sources can drive the D inputs without further logic.

Several inputs, as shown in Table 4 can modify instruction execution. The combination  $\overline{CC}$  HIGH and  $\overline{CCEN}$  LOW is used as a test in 10 of the 16 instructions.  $\overline{RLD}$ , when LOW, causes the D input to be loaded into the register/counter, overriding any HOLD or DEC operation specified in the instruction.  $\overline{OE}$ , normally LOW, may be forced HIGH to remove the Am2910 Y outputs from a three-state bus.

| HEX<br>I3-I0 MNEMONIC | ~                          | REG/<br>CNTR          | FAIL<br>CCEN = LOW and CC = HIGH |      | PASS<br>CCEN = HIGH or CC = LOW |      | REG/  |        |        |

|-----------------------|----------------------------|-----------------------|----------------------------------|------|---------------------------------|------|-------|--------|--------|

|                       | MNEMONIC                   | NAME                  | CON-<br>TENTS                    | Y    | STACK                           | Y    | STACK | CNTR   | ENABLE |

| 0                     | JZ                         | JUMP ZERO             | ×                                | 0    | CLEAR                           | 0    | CLEAR | HOLD   | PL     |

| 1                     | CJS                        | COND JSB PL           | ×                                | PC   | HOLD                            | D    | PUSH  | HOLD   | PL     |

| 2                     | JMAP                       | JUMP MAP              | X                                | D    | HOLD                            | D    | HOLD  | HOLD   | MAP    |

| 3                     | CJP                        | COND JUMP PL          | ×                                | PC   | HOLD                            | D    | HOLD  | HOLD   | PL     |

| 4                     | PUSH                       | PUSH/COND LD CNTR     | X                                | PC   | PUSH                            | PC   | PUSH  | Note 1 | PL     |

| 5                     | JSRP                       | COND JSB R/PL         | X                                | R    | PUSH                            | D    | PUSH  | HOLD   | PL     |

| 6                     | CJV                        | COND JUMP VECTOR      | ×                                | PC   | HOLD                            | D    | HOLD  | HOLD   | VECT   |

| 7                     | JRP                        | COND JUMP R/PL        | x                                | R    | HOLD                            | D    | HOLD  | HOLD   | PL     |

| 8 RFCT                | DECT                       | REPEAT LOOP, CNTR ≠ 0 | ≠0                               | F    | HOLD                            | F    | HOLD  | DEC    | PL     |

|                       | $REFEAT LOOP, CNTR \neq 0$ | = 0                   | PC                               | POP  | PC                              | POP  | HOLD  | PL     |        |

| 9                     | 9 RPCT REP                 | REPEAT PL, CNTR ≠ 0   | ≠0                               | D    | HOLD                            | D    | HOLD  | DEC    | PL.    |

| 9 NFCI                | REFERINC, CNTR #0          | = 0                   | PC                               | HOLD | PC                              | HOLD | HOLD  | PL     |        |

| A                     | CRTN                       | COND RTN              | X                                | PC   | HOLD                            | F    | POP   | HOLD   | PL     |

| В                     | CJPP                       | COND JUMP PL & POP    | X                                | PC   | HOLD                            | D    | POP   | HOLD   | PL     |

| С                     | LDCT                       | LD CNTR & CONTINUE    | ×                                | PC   | HOLD                            | PC   | HOLD  | LOAD   | PL     |

| D                     | LOOP                       | TEST END LOOP         | X                                | F    | HOLD                            | PC   | POP   | HOLD   | PL     |

| E                     | CONT                       | CONTINUE              | ×                                | PC   | HOLD                            | PC   | HOLD  | HOLD   | PL     |

| F TW                  | TWP                        | THREE-WAY BRANCH      | ≠0                               | F    | HOLD                            | PC   | POP   | DEC    | PL     |

|                       | IVVB                       | I HREE-WAT BRANCH     | = 0                              | D    | POP                             | PC   | POP   | HOLD   | PL     |

TABLE 4. Am2910 MICROINSTRUCTION SET.

The stack, a five-word last-in, first-out 12-bit memory, has a pointer which addresses the value presently on the top of the stack. Explicit control of the stack pointer occurs during instruction 0 (RESET), which makes the stack empty by resetting the SP to zero. After a RESET, and whenever else the stack is empty, the content of the top of stack is undefined until a PUSH occurs. Any POPs performed while the stack is empty put undefined data on the F outputs and leave the stack pointer at zero. Any time the stack is full (five more PUSHes than POPs have occurred since the stack usa last empty), the FULL warning output occurs. No additional PUSH should be attempted onto a full stack; if true, information at the top of the stack will be overwritten and lost.

#### THE Am2910 INSTRUCTION SET

The Am2910 provides 16 instructions which select the address of the next microinstruction to be executed. Four of the instructions are unconditional – their effect depends only on the instruction. Ten of the instructions have an effect which is partially controlled by an external, data-dependent condition. Three of the instructions have an effect which is partially controlled by the contents of the internal register/counter. The instruction set is shown in Table 4. In this discussion it is assumed that CI is tied HIGH.

In the ten conditional instructions, the result of the datadependent test is applied to  $\overrightarrow{\text{CC}}$ . If the  $\overrightarrow{\text{CC}}$  input is LOW, the test is considered to have been passed, and the action specified in the name occurs; otherwise, the test has failed and an alternate (often simply the execution of the next sequential microinstruction) occurs. Testing of  $\overrightarrow{\text{CC}}$  may be disabled for a specific microinstruction by setting  $\overrightarrow{\text{CCEN}}$  HIGH, which unconditionally forces the action specified in the name; that is, it forces a pass. Other ways of using  $\overrightarrow{\text{CCEN}}$  include (1) tying it HIGH, which is useful if no microinstruction is data-dependent; (2) tying it LOW if datadependent instructions are never forced unconditionally; or (3) tying it to the source of Am2910 instruction bit I<sub>0</sub>, which leaves instructions 4, 6 and 10 as data-dependent but makes others unconditional. All of these tricks save one bit of microcode width.

The effect of three instructions depends on the contents of the register/counter. Unless the counter holds a value of zero, it is decremented; if it does hold zero, it is held and a different microprogram next address is selected. These instructions are useful for executing a microinstruction loop a known number of times. Instruction 15 is affected both by the external condition code and the internal register/counter.

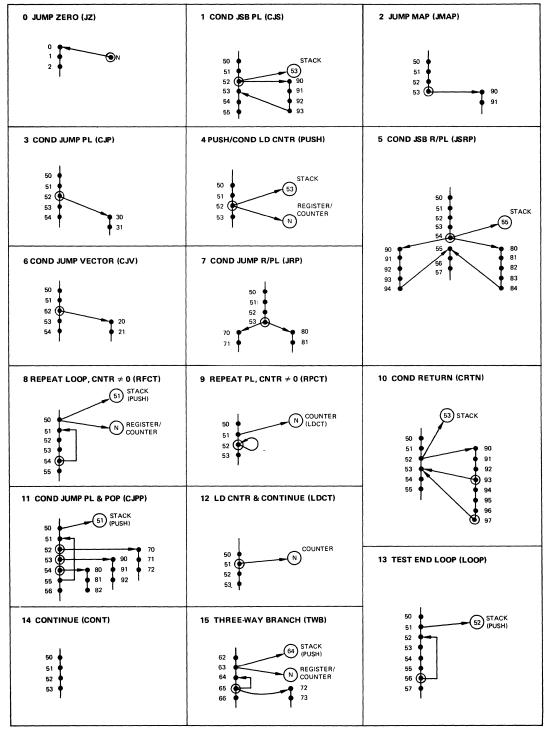

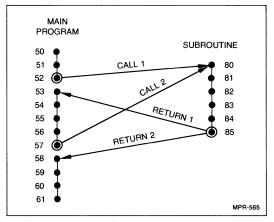

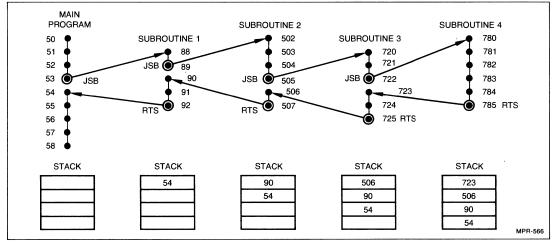

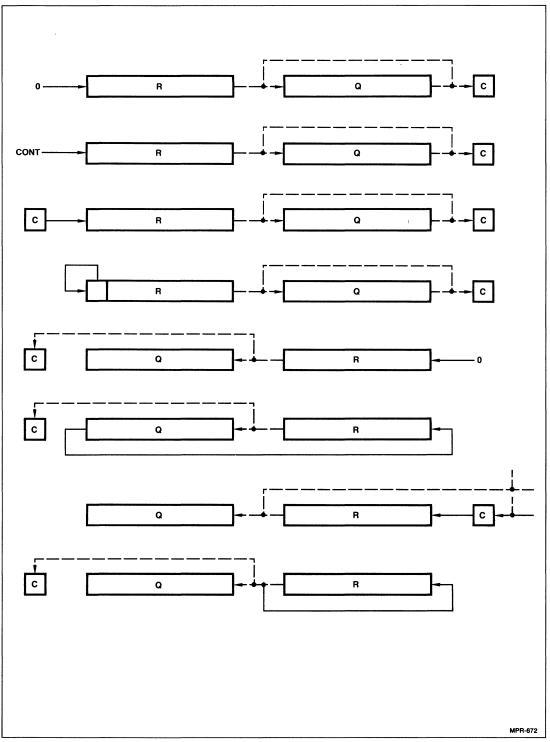

Perhaps the best technique for understanding the Am2910 is to simply take each instruction and review its operation. In order to provide some feel for the actual execution of these instructions, Figure 5 is included and depicts examples of all 16 instructions.

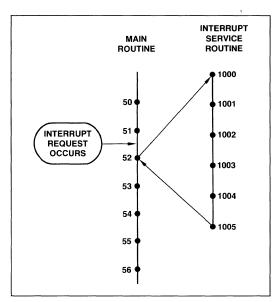

The examples given in Figure 5 should be interpreted in the following manner: The intent is to show microprogram flow as various microprogram memory words are executed. For example, the CONTINUE instruction, instruction number 14, as shown in Figure 5, simply means that the contents of microprogram memory word 50 is executed, then the contents of word 51 is executed. This is followed by the contents of microprogram memory word 52 and the contents of microprogram memory word 53. The microprogram addresses used in the examples were arbitrarily chosen and have no meaning other than to show instruction flow. The exception to this is the first example, JUMP ZERO, which forces the microprogram location counter to address ZERO. Each dot refers to the time that the contents of the microprogram memory word is in the pipeline register. While no special symbology is used for the conditional instructions, the text to follow will explain what the conditional choices are in each example.

It might be appropriate at this time to mention that AMD has a microprogram assembler called AMDASM, which has the capability of using the Am2910 instructions in symbolic representation. AMDASM's Am2910 instruction symbolics (or mnemonics) are given in Figure 5 for each instruction and are also shown in Table 4.

Instruction 0, JZ (JUMP and ZERO, or RESET) unconditionally specifies that the address of the next microinstruction is zero. Many designs use this feature for power-up sequences and provide the power-up firmware beginning at microprogram memory word location 0.

Instruction 1 is a CONDITIONAL JUMP-TO-SUBROUTINE via the address provided in the pipeline register. As shown in Figure 5, the machine might have executed words at address 50, 51 and 52. When the contents of address 52 is in the pipeline register, the next address control function is the CONDITIONAL JUMP-TO-SUBROUTINE. Here, if the test is passed, the next instruction executed will be the contents of microprogram memory location 90. If the test failed, the JUMP-TO-SUBROUTINE will not be executed; the contents of microprogram memory location 53 will be executed instead. Thus, the CONDITIONAL JUMP-TO-SUBROUTINE instruction at location 52 will cause the instruction either in location 90 or in location 53 to be executed next. If the TEST input is such that location 90 is selected, value 53 will be pushed onto the internal stack. This provides the return linkage for the machine when the subroutine beginning at location 90 is completed. In this example, the subroutine was completed at location 93 and a RETURN-FROM-SUBROUTINE would be found at location 93.

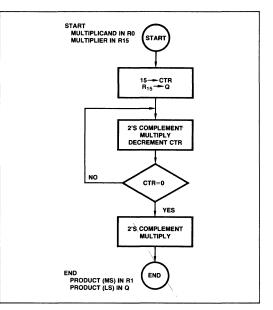

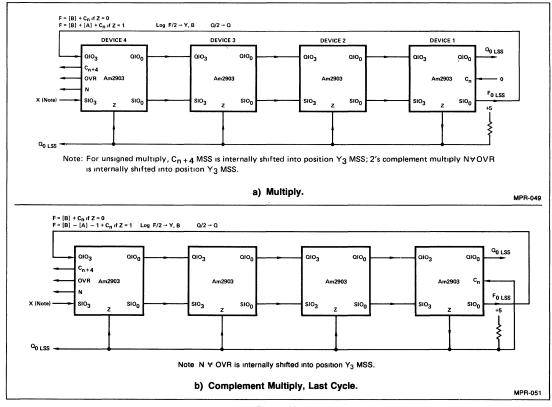

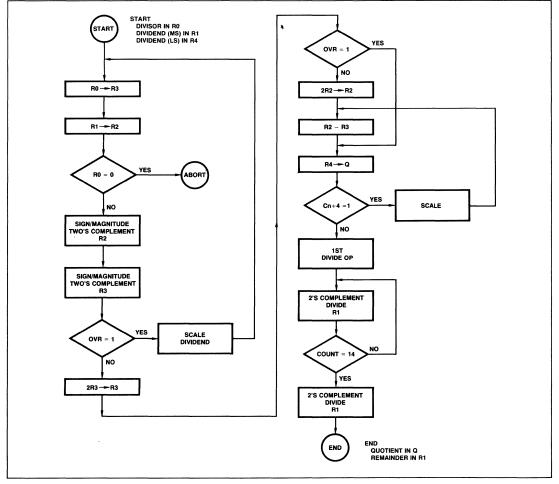

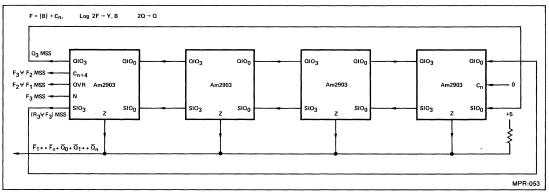

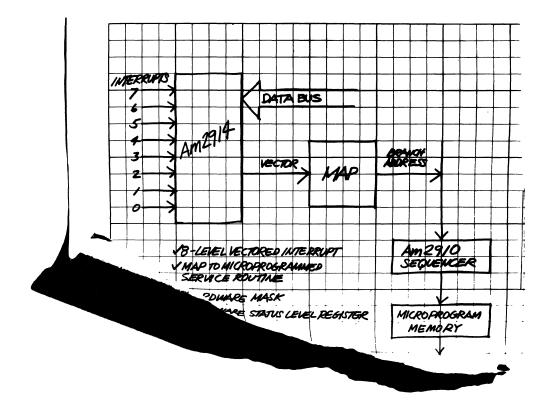

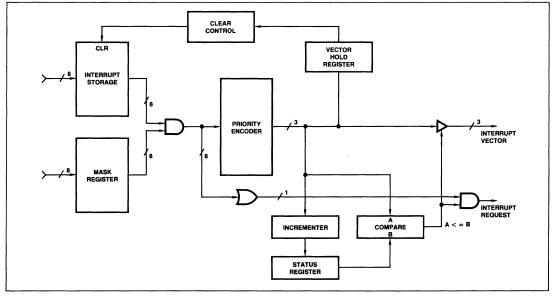

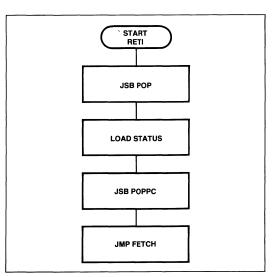

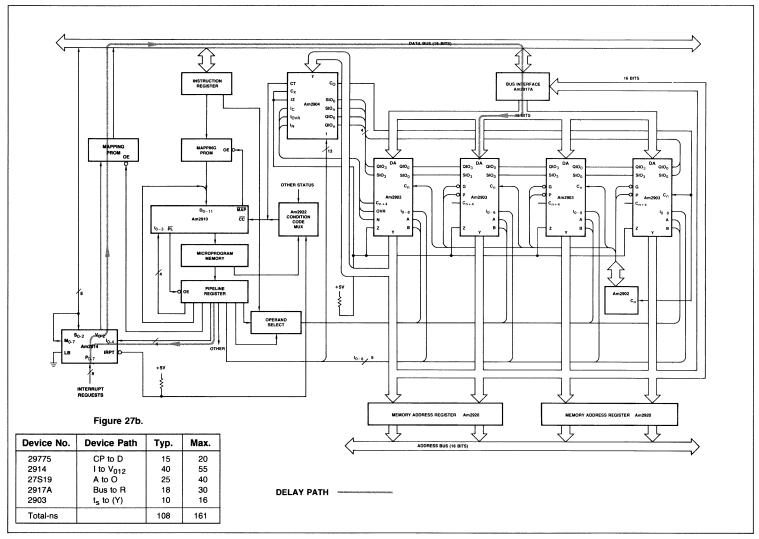

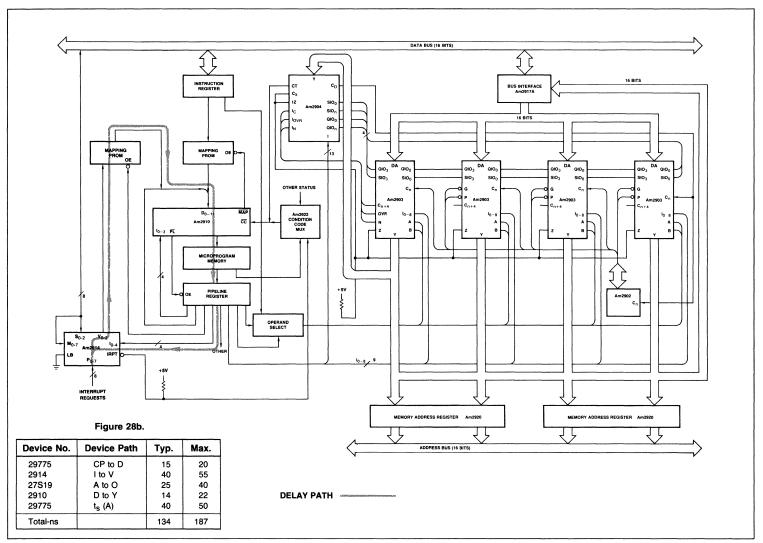

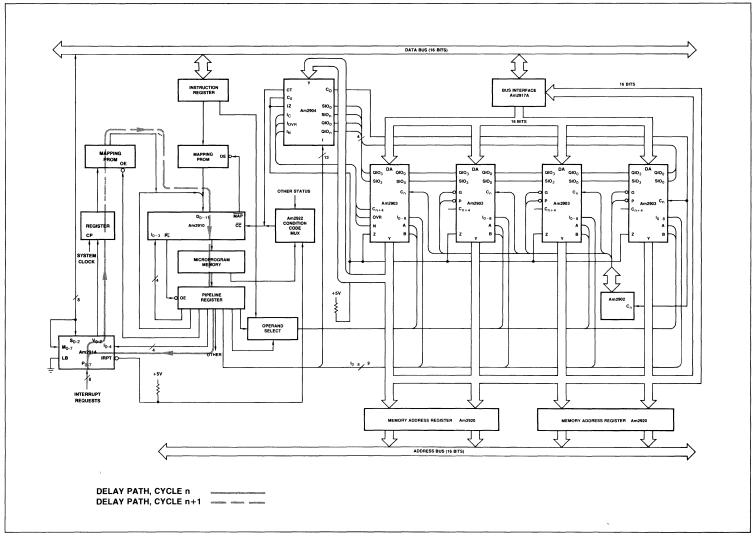

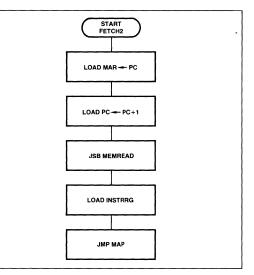

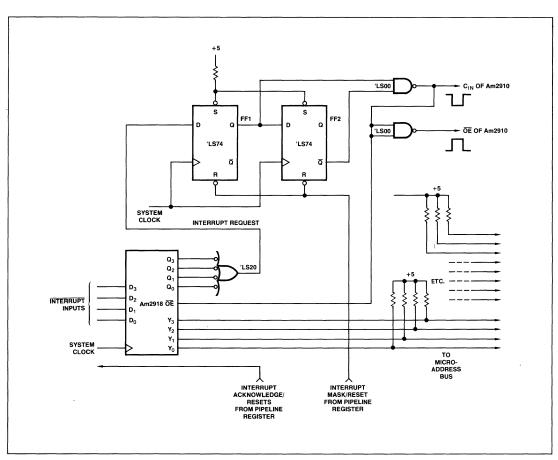

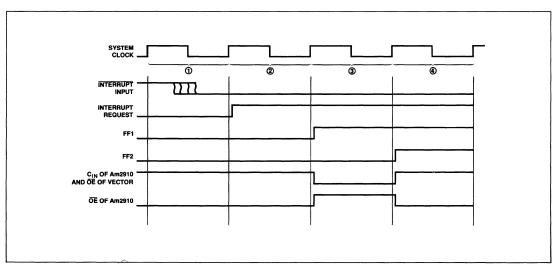

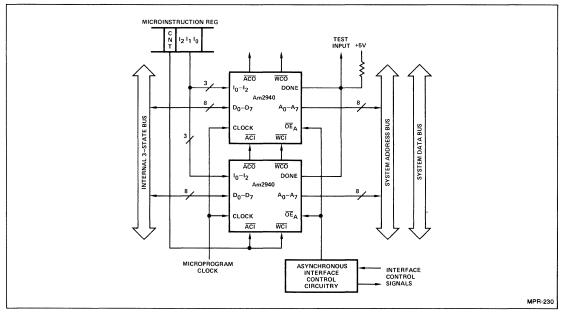

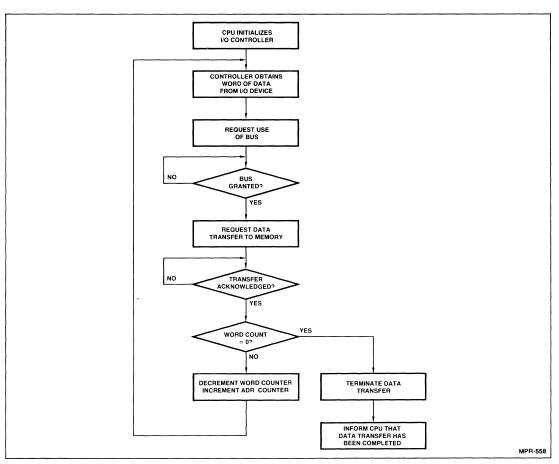

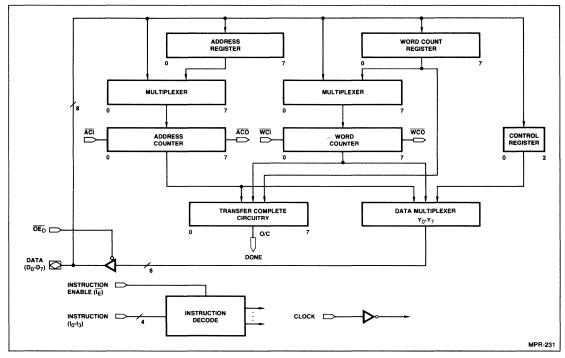

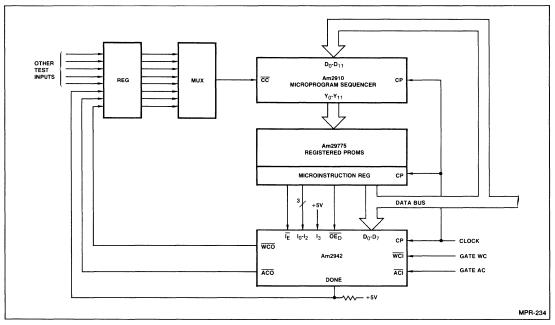

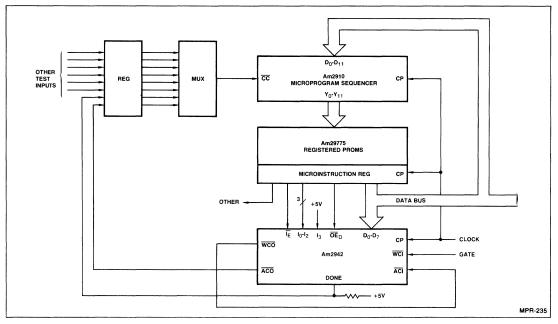

Instruction 2 is the JUMP MAP instruction. This is an unconditional instruction which causes the  $\overline{MAP}$  output to be enabled so that the next microinstruction location is determined by the address supplied via the mapping PROMs. Normally the JUMP MAP instruction is used at the end of the instruction fetch sequence for the machine. In the example of Figure 5, microinstructions at locations 50, 51, 52 and 53 might have been the fetch sequence and at its completion at location 53, the jump map function would be contained in the pipeline register. This example shows the mapping PROM outputs to be 90; therefore, an unconditional jump to microprogram memory address 90 is performed.